For More Information IEDM Online: irps.org

### **Table of Contents**

| ntro3                                        |   |

|----------------------------------------------|---|

| Committees                                   |   |

| Topics of Interest5                          |   |

| Program:                                     |   |

| Keynote & Invited Speakers6                  |   |

| Tutorials8                                   |   |

| Workshops8                                   |   |

| Year in Review9                              |   |

| Highlighted Papers10                         |   |

| Poster & Focus Sessions11                    |   |

| Exhibits & Exhibit Events11                  |   |

| Abstracts, Bios for Tutorials, Short Courses | & |

| Technical ProgramAppendix                    |   |

### Intro

For 59 years, IRPS has been the premiere conference for engineers and scientists to present new and original work in the area of microelectronics reliability. Drawing participants from the United States, Europe, Asia, and all other parts of the world, IRPS seeks to understand the reliability of semiconductor devices, integrated circuits, and microelectronic systems through an improved understanding of both the physics of failure as well as the application environment.

IRPS provides numerous opportunities for attendees to increase their knowledge and understanding of all aspects of microelectronics reliability. It is also an outstanding chance to meet and network with reliability colleagues from around the world.

IRPS is Co-Sponsored by IEEE EDS and Reliability Society

### **Digital & Social Media**

• Facebook: @IEEE-IRPS-239965161886

• Twitter: @IEEEIRPS

• LinkedIn: https://www.linkedin.com/groups/2624656/profile

YouTube: @IEEEIRPSInstagram: @ieee irps

• Weibo: http://weibo.com/u/5500677074

# Committees Executive Committee

**General Chair**

Elyse Rosenbaum

**Vice-General Chair**

Mark Porter

TPC Chair

Gaudenzio Menghesso

**TPC Vice-Chair**

Robert Kaplar

**Finance Chair**

Charlie Slayman

**Arrangements Chair**

Christine Hau-Riege

**AV Chair** Jason Ryan

**Presentation Chair**

Jason Ryan

**Publications Chair**

Susumu Shuto

**Publicity Chair**

Cathy Christiansien

**Publicity Co-Chair**

Yen-Hao Shih/Susumu Shuto

**Registration Chair**

Koji Eriguchi

**Tutorials Chair**

Yen-Hao Shih

**Workshops Chair**

Chris Connor

**Secretary**

Ben Kaczer

**Communications Chair**

Vincent Huard

### 3D/2.5D/Packaging

Chair Kothandaraman Chandrasekara

- IBM Research

Chair - Vice Sudarshan Rengarajan Amazon Lab 126

ex Chair Alan Lucero - Intel

Lucile Arnaud - CEA / LETI

Kristof Croes - IMEC

Troy L Graves-Abe - Northrup Grumman

Kangwook Lee - Amkor

Murugesan Mariappan - Tohuku U.

C S Premachandran - Global Foundries

Brian Roggeman - Qualcomm

Katsuyuki Sakuma - IBM Research

Chih-Hang Tung - TSMC

Loris Vendrame - Micron

### Circuit Reliability/Aging

Chair Chris Kim - U. of Minnesota

Chair - Vice Georgios Konstadinidis Oracle

ex Chair Vijay Reddy - Texas Instruments

Florian Cacho - STMicroelectronics

Kevin Cao - Arizona State U.

Karl Hofmann - Infineon

Kevin Huang - TSMC

Kazutoshi Kobayashi - Kyoto Institue of

Technology

Tom Kopley - ONSemiconductors

Haldun Kufluoglu - Qualcomm

Pong-Fei Lu - IBM

Jim Tschanz - Intel

## Dielectrics - Gate, MOL, BEOL

Chair Nagarajan Raghavan -Singapore U. of Tech. and Design Chair - Vice Andrew Kim - IBM ex Chair Yung-Huei Lee - TSMC Erik Bury - IMEC Kristof Croes - IMEC Martin Gall - Fraunhofer Institute Thomas Kauerauf - Samsung Electronics Mario Lanza - Soochow U. Shou Chung Lee - TSMC Joel Plawsky - Rensselaer Poly Chetan Prasad - Intel Francesco Maria Puglisi - UniMORE Tian Shen - GlobalFoundries Naohito Suzumura - Renesas Stanislav Tyaginov - TU Wien Shinji Yokogawa - UEC

### ESD/Latchup

Chair Michael Khazhinsky - Silicon Labs Chair - Vice Gianluca Boselli - Texas Instruments ex Chair Farzan Farbiz - Apple

Lorenzo Cerati - ST Microelectronics

Shih-Hung Chen - IMEC

Zhong Chen - U. of Arkansas

Harald Gossner - Intel

Timothy Maloney - Intel, Emeritus

Moto Okushima - Renesas

Mayank Shrivastava - Indian Institute of

Science

Michael Stockinger - NXP

Teruo Suzuki - Socionext Inc.

### **Failure Analysis**

Chair Kevin Johnson - Intel

Chair - Vice Baohua Niu - TSMC

ex Chair Bryan Tracy - EAG Laboratories

Jayhoon Chung - TI

Branden Foran - The Aerospace Corp.

Eckhard Langer - GlobalFoundries

Jane Li - NVidia

Ken Rodbell - IBM

William Vanderlinde - IARPA

### **Memory**

Chair Alessandro Spinelli Politecnico di Milano Chair - Vice Andrea Chimenton - Intel Bob Gleixner - Micron Ming-Yi Lee - Macronix Masahiko Nakayama - Toshiba Kab-Jin Nam - Samsung Hokyung Park - SKHynix Luca Perniola - CEA Cristian Zambelli - U. of Ferrara

### **Metallization Reliability**

Chair Gavin Hall - ON Semi Chair - Vice Zsolt Tokei - IMEC Matsuyama Hideya - Socionext Sumit Kapadia - Intel Ki-Don Lee - Samsung Baozhen Li - IBM Ming-Hsien Lin - TSMC Yu-Lin Shen - U. of New Mexico Takamasa Usui - Toshiba

#### **Photovoltaics**

Chair Michael Daenen - Hasselt U. Chair - Vice Karl-Anders Weiss Fraunhofer - ISE ex Chair Andrea Cester - UniPD Neelkanth G Dhere - U. of Central Florida Cosimo Gerardi - ENEL Suren Gevorgyan - DTU Salvatore Lombardo - IMM-CNR Mirjam Theelen - Solliance Koen Vandewal - IAPP Eszter Voroshazi - IMEC Shenghao Wang - OIST Martin Weis - STUBA

### **Process Integration**

Chair Xavier Garros CEA - LETI

Chair - Vice Barry Linder - IBM

ex Chair Andreas Kerber - Global

Foundries

Adrian Chasin - IMEC

Minjung Jin - Samsung

Siddarth Krishnan - Applied materials

Jen-Hao Lee - TSMC

Hiroshi Miki - Hitachi

Mustapha Rafik - ST Microelectronics

Anisur Rahman - Intel

Guido Sasse - NXP

### **Product Reliability**

Chair Brian Pedersen - Intel

Chair - Vice Pierre Chor-Fung Chia Cisco

John Agness - Rohm Semi

Jae-Gyung Ahn - Xilinx

Minhyeok (MH) Choe - Samsung

Chang Yeol (CY) Lee - SK Hynix

Shou-En Liu - Mediatek

Souhir Mhira - STmicroelectronic

Steven Mittl - IBM

Homi Mogul - Qualcomm

Balaji Narasimham - Broadcom Limited

J. R. Shih - TSMC

Kong Boon Yeap - Global Foundries

### **Reliability Testing**

Shih-Chang Chen - TSMC

Chair - Vice Derek Slottke - Intel

ex Chair Hosain Farr - Qualitau

Jifa Hao - On Semiconductor

Robert Higgins - Texas Instruments

Stéphane Moreau - CEA-Leti

Fiorella Pozzobon - STMicroelectronics

Bryan Root - Celadon Systems

Dirk Rudolph - GlobalFoundries

Pascal Salome - Serma Technologies

Tim Turner - Xact/Texas Semicon Labs

Yi Zhao - Zhejiang U.

#### **Soft Error**

Chair Marta Bagatin - U. of Padova Chair - Vice Nihaar Mahatme - NXP Semiconductors ex Chair Balaji Narasimham - Broadcom Thiago Assis - RCI Bharat Bhuva - Vanderbilt U. Ethan Cannon - Boeing Indranil Chatterjee - Airbus Adrian Evans - iRoC Matthew Gadlage - NAVSEA Crane Gilles Gasiot - STMicroelectronics Shah Jahinuzzaman - Intel Michael King - Sandia Labs Daisuke Kobayashi - JAXA Phil Oldiges - IBM Taiki Uemura - Samsung Haibin Wang - Hohai U. Shi-Jie Wen - Cisco

### **System Reliability**

Chair Guneet Sethi - Amazon Lab 126 Chair - Vice Rob Kwasnick - Intel ex Chair Randy - Crutchfield Medtronic Ajay Kamath - Google Heejin Kim - Samsung Display (Development Quality and Reliability Group) Bob Knoell - NXP Semiconductors Pradeep Lall - Auburn U. Amit Marathe - Google Jay Sarkar - Western Digital Yanos Sazeides - U. of Cyprus David Sunderland - Boeing (Retired)

## Transistors/Beyond CMOS

Chair Steve Ramey - Intel Chair - Vice Tibor Grasser - TUWien ex Chair Souvik Mahapatra - India Institute of Technology Jason Campbell - NIST Eun-Ae Chung - Samsung Suman Datta Norte Dame U. Xavier Federspiel - STMicroelectronics Jacopo Franco - IMEC Luca Larcher - U. of Modena Chris Liu - Huawei Souvik Mahapatra - India Institute of Technology Montserrat Nafria - U. Autonoma de Barcelona Jurriaan Schmitz - U. of Twente Ricki Southwick - IBM Purushothaman Srinivasan -Globalfoundries Bonnie Weir - Broadcom Chad Young - UT

### **Wide Band Gap**

Chair Sandeep Bahl - TI Chair - Vice Matteo Meneghini - U. Padova ex Chair Denis Marcon - IMEC GaNSPEC Liaison Robert Kaplar -Sandia labs Abhishek Banerjee - ON Alberto Castellazzi - U. Nottingham Ferdinando Iucolano - ST Tsunenobu Kimoto - Kyoto U. Martin Kuball - U. Bristol Aivars Lelis - US Army Research Labs Peter Losee - GE David Sheridan - AOS Kurt Smith - Transphorm Steve Stoffels - IMEC Kenichiro Tanaka - Panasonic Deepak Veereddy - Infineon Shireen Warnock - MIT Lincoln labs

# Topics of Interest SPECIAL FOCUS TOPICS

IRPS18 is soliciting increased participation in the following areas: reliability of wide bandgap semiconductor power devices, circuit aging, consumer electronics, reliability of 2D NAND flash replacement technologies, 2.5D & 3D packaging

### Circuits, Products, and Systems

**Circuit Reliability -** Includes digital, mixed-signal, power and RF applications; design for reliability, variability-aware design **Circuit Aging Simulation** – Includes compact modeling; statistical methods

Product IC Reliability - Includes burn-in; defect detection; on-chip sensors; modeling

Consumer Electronics Reliability - Includes smart phones; wearable devices; tablets; healthcare devices

**Electronic System Reliability** – Includes automotive, space, communications, medical, energy, and photovoltaic applications; screening techniques; reliability-aware circuit design and optimization, system monitoring; failure root cause determination; modeling methodologies, product qualification vs reliability

Soft Errors - Includes neutron and alpha particle SER; multi-bit SER/SEU; mitigation techniques; simulation

**ESD and Latchup** – Includes component and system-level ESD design; modeling and simulation

**3D Assembly** – Includes multichip modules; 3D integration with TSV; thermomechanical stress; wafer thinning effects

**Packaging** – Includes chip-package interaction; fatigue; power dissipation issues, Reliability 2.5D and 3D IC packaging and interconnects

Reliability Testing - Includes reliability equipment, tools, and test methods

### Materials, Processing, and Devices

**Transistors –** Includes hot carrier phenomena; BTI; RTN; advanced transistor scaling, variability, Ge and III-V channels **Gate Dielectrics** – Includes TDDB modeling; reliability of novel gate dielectrics; modeling of progressive breakdown; gate dielectric reliability for III-V FETs

**Beyond CMOS Devices** – Includes reliability of tunnel FETs, transistors with 2D semiconductors (graphene, MoS2), Ferroelectric FETs, and spintronics

Wide bandgap semiconductors (WBG) – Includes reliability of WBG-based power devices (GaN, SiC, Ga2O3)

**Compound and Optoelectronic devices** – includes reliability of III-V-based devices, optoelectronics devices, silicon photonics, far infrared detectors

**Back-End Reliability** – Includes Electromigration; Joule heating; stress migration; low-k dielectric breakdown; middle-of-the-line reliability, MIM/MOM capacitors

Process Integration – Includes new process-related reliability issues; foundry reliability challenges

Failure Analysis – Includes evidence of new failure mechanisms; advances in failure analysis techniques

Memory Reliability - Includes DRAM and NVM, novel memory devices: 3D Flash and ReRAM

Photovoltaics – Includes reliability of solar cell devices in silicon, CdTe, CIGS, organics, multi-junctions, etc.

MEMS – Includes reliability of sensors and actuators; reliability testing; analysis & modeling, BioMEMS

### **Program**

NOTE – For full Program, including Abstracts and Speaker information, view Appendix VIDEOS – https://www.youtube.com/user/IEEEIRPS/videos

### **Keynote & Invited Speakers**

# First Keynote: The Road to Resilient Computing in Autonomous Driving is Paved with Redundancy

Dr. Nirmal Saxena, NVIDIA

8:45 AM, Tuesday March 13th

Abstract: Deep neural networks use the computational power of massively parallel processors in applications such as autonomous driving. Autonomous driving demands resiliency (as in safety and reliability) and trillions of operations per second of computing performance to process sensor data with extreme accuracy. This keynote examines various approaches to achieve resiliency in autonomous cars and makes the case for design diversity based redundancy.

Biography: Nirmal R. Saxena is currently a distinguished engineer at NVIDIA and is responsible for HPC and automotive resilient computing. From 2011 through 2015, Nirmal was associated with Inphi Corp as CTO for Storage & Computing and with Samsung Electronics as Sr. Director working on fault-tolerant DRAM memory and storage array architectures. During 2006 through 2011, Nirmal held roles as a Principal Architect, Chief Server Hardware Architect & VP at NVIDIA. From 1991 through 2009, he was also associated with Stanford University's Center for Reliable Computing and EE Department as Associate Director and Consulting Professor respectively. During his association with Stanford University, he taught courses in Logic Design, Computer Architecture, Fault-Tolerant Computing, supervised six PhD students and was co-investigator with Professor Edward J. McCluskey on DARPA's ROAR (Reliability Obtained through Adaptive Reconfiguration) project. Nirmal held senior technical and management positions at Alliance Semiconductors, Chip Engines, Tiara Networks, Silicon Graphics, Hal Computers, and Hewlett Packard.

Nirmal received his Ph.D. EE degree (1991) from Stanford University. He is a Fellow of the IEEE (2002) and was cited for his contributions to reliable computing.

# Second Keynote: Reliable Ultra-Low Energy Security Circuit Primitives for IoT Edge Systems

Dr. Sanu Mathew, Intel Corporation

9:30 AM, Tuesday March 13th

Abstract: Low-area energy-efficient security primitives are key building blocks for enabling end-to-end content protection, user authentication and data security in IoT platforms. This talk describes the design of reliable security circuit primitives with optimal arithmetic for seamless integration into area/battery constrained IoT systems: 1) A 2040-gate AES accelerator achieving 289Gbps/W efficiency in 22nm CMOS, 2) Hardened hybrid Physically Unclonable Function (PUF) circuit to generate a 100% stable encryption key. The talk will also discuss design issues related to side-channel leakage of embedded secret keys, and how they may be addressed during design of encryption circuits. We will also discuss the effect of aging on PUF circuits and techniques to handle aging issues over the lifetime of the die.

Biography: Sanu Mathew is a Senior Principal Engineer with the Circuits Research Labs at Intel Corporation, Hillsboro, Oregon, where he leads research and development of energy-efficient hardware accelerators for encryption and security. Sanu obtained his Ph.D. degree in Electrical and Computer Engineering from State University of New York at Buffalo in 1999. He holds 41 issued patents, with another 63 patents pending and has published over 77 conference/journal papers. He has been with Intel for the past 18 years. Sanu is a Fellow of the IEEE.

### **Invited Speakers**

- The effects of radiation on the terrestrial operation of SiC MOSFETs Bakin Akturk, CoolCAD

- Reliability Challenges in 2.5D Packaging and Embedded Silicon Bridge Emre Armagan, Intel

- Protective nanometer films for reliable Cu-Cu connections Berthold, Fraunhofer

- p-GaN gate reliability including short-circuit robustness Alberto Castelazzi, Univ. Nottingham

- SiC Power MOSFET Gate Oxide Breakdown Reliability Current Status Charles Cheung, NIST

- Reliable and damage-resistant optics and detectors for x-ray free-electron lasers Stefan Hau-Riege, Lawrence National Laboratory

- Next Generation Interconnect Reliability Metallization Integration Chao-Kun Hu, IBM

- Reliability of MEMS sensors through self calibration Amit Lal, Cornell University

- Reliability Studies of SiC Vertical Power MOSFETs Daniel J. Lichtenwalner, Wolfspeed

- Exascale Fault Tolerance Challenge and Approaches Cameron McNairy, Intel

- Reliability issues of GaN commercialization Umesh Mishra, UC Santa Barbara

- Cathodoluminescence spectroscopy for failure analysis and process development of GaN-based microelectronic devices Christian Monachon, Attolight

- COTS Electronics Reliability for Space Applications Jonny Pellish, NASA

- System level ESD and its implications on I/O protection David Pommerenke, Missouri University of Science and Technology

- Reliability Challenges on 2.5D/3D chip integration an Overview C S Premachandran, Global Foundries

- Airplane Systems Design for Reliability & Quality Anapathur Ramesh, Boeing

- Recent Advances in In-situ and In-field Aging Monitoring and Compensation for Integrated Circuits Mingoo Seok,

Columbia University

- Role of electron and hole trapping in degradation and breakdown of oxide films Alex Shluger, University College,

- Permanent shunting from passing shadows: Reverse-bias damage in thin-film photovoltaic modules Timothy Silverman,

NREL

- Defects Affecting SiC Power Device reliability Bob Stahlbush, NRL

- The Physics of NBTI: What Do We Really Know? Jim Stathis, IBM

- Estimating transistor channel temperature using time-resolved and time-integrated NIR photoemission Franco Stellari,

IBM

- Reliability perspective of resistive synaptic devices on the neuromorphic system performance Shimeng Yu, Arizona State University

### **Distinguished Lecturer**

#### Real Limits to Nanoelectronics: Interconnects and Contacts

Prof. Krishna Saraswat, Stanford University

1:30 PM, Wednesday March 14th

Abstract: As device scaling continues, parasitic source resistance largely dominated by contact resistance is beginning to limit the device performance. While novel structures and materials have enhanced the transistor performance, the opposite is true for the interconnects that link these transistors. This talk will address effects of scaling on the performance of conventional contacts and interconnects, and explore alternate contact and interconnect schemes

Biography: Prof. Krishna Saraswat is Rickey/Nielsen Professor in the School of Engineering, Professor of Electrical Engineering and by courtesy Professor of Materials Science & Engineering at Stanford University.

He received his B.E. degree in Electronics in 1968 from BITS, Pilani, India, and his M.S. and Ph.D. degrees in Electrical Engineering in 1969 and 1974 respectively from Stanford University, Stanford, CA. During 1969-70, he worked at Texas Instruments. After graduating he joined Stanford University as a Research Associate in 1975 and later became a Professor of Electrical Engineering in 1983. He also has an honorary appointment of an Adjunct Professor at BITS, Pilani, India since January 2004.

His research interests are in new and innovative materials, structures, and process technology of silicon, germanium and III-V devices and interconnects for VLSI and nanoelectronics. Areas of his current interest are: new device structures to continue scaling MOS transistors and memories to nanometer regime, 3-D ICs, optical interconnections and high efficiency and low cost solar cells.

He has supervised more than 85 doctoral students, 30 post doctoral scholars and has authored or co-authored 15 patents and over 790 technical papers. He is a Life Fellow of the IEEE. He received the Thomas Callinan Award from The Electrochemical Society in 2000, the 2004 IEEE Andrew Grove Award, Inventor Recognition Award from MARCO/FCRP in 2007, the Technovisionary Award from the India Semiconductor Association in 2007, BITS Pilani Distinguished Alumnus Awards in 2012 and the Semiconductor Industry Association Researcher of the Year Award in 2012. He is listed by ISI as one of the Highly Cited Authors in his field.

### **Tutorials**

- Semiconductor Reliability and Product Qualification Chris Henderson, Semitracks

- Soft Error Fundamentals Norbert Seifert, Intel

- FEOL Reliability Barry Linder, IBM

- Introduction to ESD and Latchup Design and Test Methods Nathan Jack, Intel

- Back-End of Line (BEOL) Reliability Baozhen Li, IBM

- Testing of Automotive IC's: Introduction and Advances Davide Appello, STMicroelectronics

- An Overview of Chip to Package Interaction and its Impact on Reliability Scott Pozder, GLOBALFOUNDRIES

- System Reliability Amit Marathe and Amit Kale, Google

- Self-Heating in 10nm-class FinFET Chetan Prasad / Intel

- STT-MRAM: Past History, Current Status and Future Perspectives Yiming Huai / Avalanche

- Ultra High Voltage LDMOS Device and Technology Sameer Pendharkar, Texas Instruments

- Advanced BTI Tibor Grasser, Univ. of TU Wien

- 3D Flash Memories: Overview of Cell Structures, Operations and Reliability Makoto Fujiwara, Toshiba

- SiC Power MOSFETs: Application Benefits and Technology Validations Needs Albert Castellazzi, Nottingham University

- Conductive Atomic Force Microscopy and its Use in Nanoelectronic Device Reliability Mario Lanza, SUDA

- HBM Design, Test & Reliability Challenges for AI Applications Daeyong Shim, SKHynix

- Validating the Robustness of GaN Power Transistors Kenichiro Tanaka, Panasonic

### **Workshops**

- 3D Transistor reliability Hot Carrier Chetan Prasad (INTEL) / Jacopo Franco (IMEC)

- Providing Enterprise-level System Reliability in the sub-10nm technology era Ron Newhart (IBM) / Cameron McNairy (Intel)

- Emerging-memory-reliability-challenges and opportunities-in-MRAM, RRAM, 3D XP Jon Slaughter (IBM) / Jerry Chung Wei Hsu (TSMC)

- Automotive: What are the challenges for new technologies? Andreas Aal (VW) / Khai Nguyen (NVIDIA) / Shalabh Tandon (Intel)

- Circuit-Reliability-advanced-nodes-concerns and CAD tools flow Matthew Hogan (Mentor) / Wonjae Kang (Intel) / Hiu Wong (Synopsys)

- GaN reliability for power and RF devices What are the key issues and how to resolve? Sandeep Bahl (TI) / Matteo Meneghini (U of Padova)

- Challenges and advances in advance node interconnect reliability Patrick Justison (Global Foundries) / Rahim Kasim

(Intel)

- 3D Transistor reliability: BTI Souvik Mahapatra (IIT Bombay) / Chadwin Young (University of Texas at Dallas)

- Storage and Memory SSD, SD, DIMM: Resiliency in design, system-level considerations and role of usage analytics -Jay Sarkar (Western Digital - HGST) / Haitham Hamed (SK Hynix)

- Synergies between GaN and SiC for reliability development and standardization Sameh Khalil (Infineon) / Aivars Lelis (U.S. Army Research Laboratory )

- Advanced packaging reliability: 2.5D, 3D and fan-out packaging for system scale Kangwook Lee (Amkor) / Emre Armagan (Intel)

- Circuit Reliability: In-field healing and repair serious need or science fiction? Jim Tschanz (Intel) / Alain Bravaix (ISEN-IM2NP & STM)

### **Year In Review**

### GaN and SiC Device Reliability Year-in-Review

**GaN** – 2017 was an important year for GaN, with product and technology announcements, the establishment of the JEDEC JC70 WBG standards committee, of progress in reliability physics and continued innovation in device design. We will review highlights from papers that are helping develop our reliability physics foundation, papers on device innovation and of a new loss mechanism important for future application usage.

**SiC** – Enabling progress towards (widespread) commercialisation: SiC advances in material, devices, package and application. In recent years, SiC technology has transitioned from being essentially a research focus area to showing credible promise as a commercial reality. This presentation will review key advances and results presented in 2017, which play a key role in enabling this important transition. The review will cover the whole range of underpinning development areas, from material and process to device design, bespoke package development and applications.

**Sandeep Bahl** is a distinguished member of technical staff in the High Voltage Power Business Unit of Texas Instruments. He has extensive experience with semiconductor technology development, and has worked on both silicon and compound semiconductor technologies. His present focus is to bring reliable GaN products to market, and to develop the methodology to know that they will be reliable under actual-use conditions. Sandeep helped kickoff the standardization effort of the GaN industry and is presently participating on the JC70 reliability committee as a task-group co-chair. He has served as chair of the Power and Compound Semiconductor subcommittee of the International Electron Devices meeting (IEDM) and of his local San Francisco/Santa Clara valley IEEE chapter. He is presently serving as chair of the IRPS Wide Bandgap Committee. Sandeep graduated with a PhD in Electrical Engineering from the Massachusetts Institute of Technology.

**Alberto Castellazzi** is an Associate Professor of Power Electronics at the University of Nottingham, UK. He has been active in power electronics R&D for over 15 years, collaborating with some of the main industrial and academic institutes worldwide. His research interests are power devices and the enabling technologies of power electronics. He has published over 180 papers in peer reviewed journals and conference proceedings and is a member of the Technical Program Committee of the IRPS, ISPSD, ESREF, ESTC and IPEC conferences.

### **MOL and BEOL Dielectrics Reliability Year-in-Review**

Studies published in 2017 with respect to MOL and BEOL dielectrics will be reviewed. First, we will focus on studies addressing the understanding of different degradation mechanisms in MOL and BEOL dielectrics, both with respect to leakage current degradation as well as time to breakdown, where intrinsic dielectric breakdown needs to be decoupled from extrinsic like metal contamination, moisture, etc. Second, we will review work where proposals are made to deal with all kinds of variability issues like LER, L2L-variations and V2L-variations. As dielectric breakdown/metal drift is also a heavily studied phenomenon in FEOL and RRAM, a few learnings from these fields which are useful for MOL and BEOL will be cited as well.

**Kristof Croes** received his BSc in physics at the Catholic University of Louvain (Belgium) in 1993 and his MSc in biostatistics at the Limburgs Universitair Centrum (LUC) in 1994. In 1999, he obtained his PhD, concerning the development of statistical techniques for planning reliability experiments. After that, he joined the reliability business unit of XPEQT, first as the software responsible and then as the manager of the R&D. From 2003 till end 2006, he was product and application manager of the package level reliability products of the Singaporean based company Chiron holdings. Beginning 2007, he went back to research, working as a BEOL reliability engineer in imec. Currently, he is group leader of the Reliability, Electrical test and Modeling group working on test, characterization (electrical, thermal and (thermo)-mechanical) and reliability with main focus on advanced interconnects (2D, 3D, OIO). Kristof was an (invited/tutorial) speaker at several leading egde semi-conductor conferences (IRPS, IITC, IEDM, ...). He also (co)-authored >100 papers in the field of reliability.

### Circuit Reliability Year-in-Review

This session will focus on the past year of research in the following areas:

- 1. Unreliable issues at advanced technology nodes: layout, manufacturability, etc.

- 2. Monitoring and adaptive design techniques at the circuit level;

- 3. System techniques for energy-efficient reliable design;

- 4. On-chip machine learning in reliable design

**Yu Cao** received the B.S. degree in physics from Peking University in 1996. He received the M.A. degree in biophysics and the Ph.D. degree in electrical engineering from University of California, Berkeley, in 1999 and 2002, respectively. He is now a Professor of Electrical Engineering at Arizona State University, Tempe, Arizona. He has published numerous articles and two books on nanoscale CMOS design. His research interests include physical design of nanoelectronics, design solutions for reliability, and hardware integration for on-chip learning. He is an IEEE Fellow.

### **Highlighted Papers**

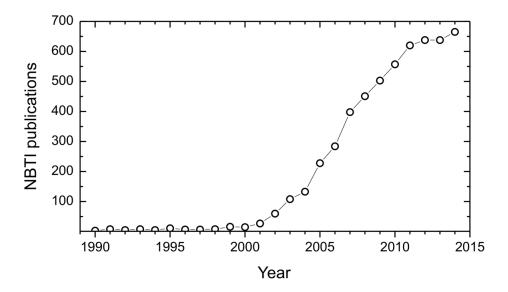

- 2A.1 Transistor The Physics of NBTI: What Do We Really Know? Jim Stathis, IBM

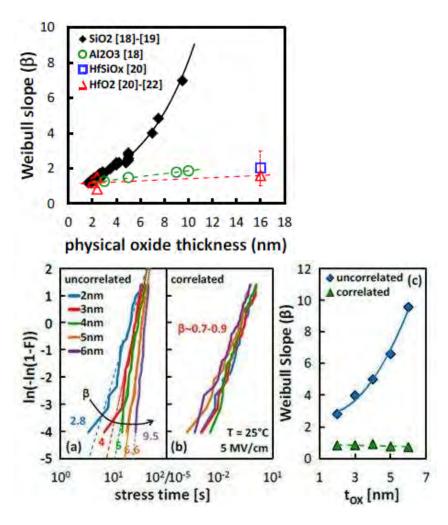

- 3A.2 Dielectrics Time-Dependent Dielectric Breakdown Statistics in SiO2 and HfO2 Dielectrics: Insights from a Multiscale Modeling Approach Andrea Padovani and Luca Larcher, MDLSoft, Inc.

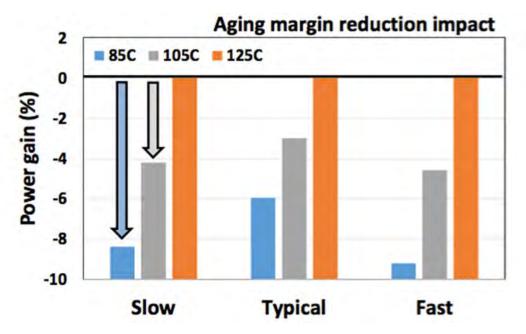

- 3C.1 Managing electrical reliability in consumer systems for improved energy efficiency Vincent Huard, Souhir Mhira, Antony Barclais, Xavier Lecocq, Fabien Raugi, Marie Cantournet and Alain Bravaix, STMicroelectronics and ISEN-REER

- 3C.6 Systems Machine Learning Based Dynamic Cause Maps for Condition Monitoring and Life Estimation Jay Sarkar, Cory Peterson, Amir Sanayei, Western Digital Corporation

- 3D.1 Products Resilient automotive products through process, temperature and aging compensation schemes Souhir Mhira, Vincent Huard, Deepak-kumar Arora, Philippe Flatresse and Alain Bravaix, STMicroelectronics, SOITEC and ISEN-REER

- 3E.1 ESD/Latch-Up Defect-Assisted Safe Operating Area Limits and High Current Failure in Graphene FETs Nagothu Karmel Kranthi, Abhishek Mishra, Adil Meersha, Harsha Variar and Mayank Shrivastava, Indian Institute of Science

- 4A.1 Dielectrics Mechanism of Soft and Hard Breakdown in Hexagonal Boron Nitride 2D Dielectrics Alok Ranjan, Nagarajan Raghavan, Sean O' Shea, Sen Mei, Michel Bosman, Kalya Shubhakar and Kin Leong Pey, Singapore University of Technology and Design and A \*STAR

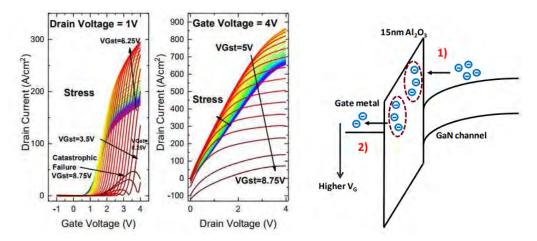

- 4B.1 Wide Band Gap Degradation of Vertical GaN FETs Under Gate and Drain Stress Maria Ruzzarin, Matteo Meneghini, Carlo De Santi, Min Sun, Tomas Palacios, Gaudenzio Meneghesso and Enrico Zanoni, University of Padova, Massachusetts Institutute of Technology

- 4C.1 Soft Error Scaling Trends and Bias Dependence of the Soft Error Rate of 16 nm and 7 nm FinFET SRAMs Balaji Narasimham, Saket Gupta, Dan Reed, J. K. Wang, Nick Hendrickson and Hasan Taufique, Broadcom

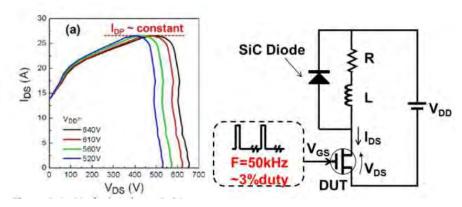

- 4E.2 Wide Band Gap Lifetime evaluation for Hybrid-Drain-embedded Gate Injection Transistor (HD-GIT) under practical switching operations - Ayanori Ikoshi, Masahiro Toki, Hiroto Yamagiwa, Daijiro Arisawa, Masahiro Hikita, Kazuki Suzuki, Manabu Yanagihara, Yasuhiro Uemoto, Kenichiro Tanaka and Tetsuzo Ueda, Automotive and Industrial Systems Company, Panasonic Corporation

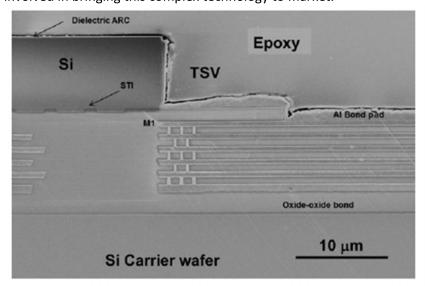

- 5B.6 2.5D/3D / packaging Device Reliability for CMOS Image Sensors with Backside TSVs Jeff Gambino, Hamid Soleimani, Irfan Rahim, Brandon Riebeek, Lieyi Sheng, Hung Truong, Gavin Hall, Rick Jerome and David Price, ON Semiconductor

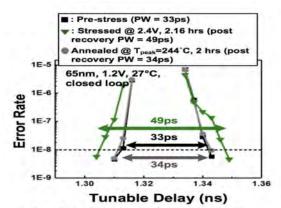

- 5C.2 Circuits All-Digital PLL Frequency and Phase Noise Degradation Measurements Using Simple On-Chip Monitoring Circuits - Gyusung Park, Bongjin Kim, Minsu Kim, Vijay Reddy and Chris H. Kim, University of Minnesota, Texas Instruments

- 5C.3 Circuits Design of Aging Aware 5 Gbps LVDS Transmitter for Automotive Applications Srikanth jagannathan, Kumar Abhishek, Tarun Goyal, Nihaar Mahatme, Gayathri Bhagavatheeswaran and Ender Yilmaz, NXP Semiconductors

- 6B.1 Failure Analysis Solving Critical Issues in 10nm Technology using Innovative Laser-based Fault Isolation and DFT Diagnosis Techniques - Lesly Zaren Endrinal, Rakesh Kinger, Lavakumar Ranganathan and Amit Sheth, Qualcomm Technologies, Inc.

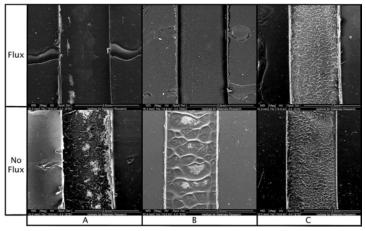

- 6C.4 Photovoltaics Mechanical and chemical adhesion at the encapsulant interfaces during the lamination of photovoltaic modules - Philippe Nivelle, Tom Borgers, Eszter Vöröshazi, Jef Poortmans, Jan D'Haen, Ward De Ceuninck and Michaël Daenen, University Hasselt

- 6D.5 Memory Reliability Benefits of a Metallic Liner in Confined PCM Wanki Kim, Yujun Xie, Yerin Kim, Takeshi Masuda, Sangbum Kim, Robert Bruce, Fabio Carta, Gloria Fraczak, Asit Ray, Koukou Suu, Chung Lam, Matt BrightSky, Judy Cha and Yu Zhu, IBM, ULVAC Inc., Yale University

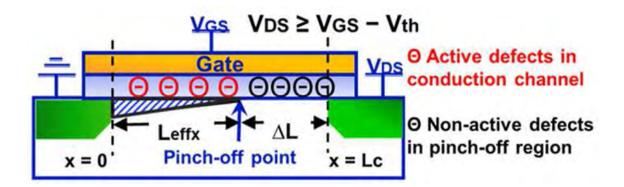

- 6E.1 Testing Lateral Profiling of HCI Induced Damage in Ultra-Scaled FinFET Devices with Id-Vd Characteristics -Miaomiao Wang, Richard Southwick, James Stathis and Kangguo Cheng, IBM

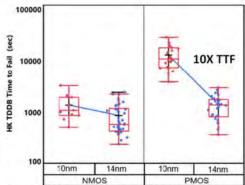

- 6F.4 Process Integration Reliability Studies of a 10nm High-performance and Low-power CMOS Technology Featuring 3rd Generation FinFET and 5th Generation HK/MG - Anisur Rahman, Javier Dacuna Santos, Pinakpani Nayak, Gerald S Leatherman and Stephen M Ramey, Intel Corporation

### Poster & Focus Sessions

See Appendix – Full Program for Poster & Focus Sessions

### Exhibits & Exhibit Events

Exhibits are an integral part of the International Reliability Physics Symposium. Don't miss this opportunity to showcase your company's products and services in our VIRTUAL exposition.

### IRPS gratefully acknowledges the generous support of our 2021 exhibitors:

Instruments

Zurich

#### Session 2A - Transistors: Models and Characterization

Session Chairs: Steve Ramey, Intel, Tibor Grasser, TUWien

Tuesday, March 13

10:35 AM - Session Introduction

10:40 AM

2A.1 The Physics of NBTI: What Do We Really Know? (Invited)

Jim Stathis, IBM

11:05 AM

## 2A.2 Characterization and Physical Modeling of the Temporal Evolution of Near-Interfacial States Resulting from NBTI/PBTI in nMOS/pMOS

T. Grasser, B. Stampfer, M. Waltl, G. Rzepa, K. Rupp, F. Schanovsky\*, G. Pobegen\*\*, K. Puschkarsky\*\*\*, H. Reisinger, B. O'Sullivan#, and B. Kaczer#, TU Wien, \*Global TCAD Solutions, \*\*KAI, \*\*\*Infineon, #imec

We use detailed CV/GV measurements to study NBTI/PBTI in nMOS/pMOS transistors. We extract a unique defect band inside the SiO2 insulator, which can describe the build-up of interfacial states over time in all four combinations using our recently suggested hydrogen release model.

11:30 AM

### 2A.3 Self-heating-aware CMOS Reliability Characterization Using Degradation Maps

E. Bury, A. Chasin, B. Kaczer, K. Chuang, J. Franco, M. Simicic, P. Weckx, D. Linten, imec

Based on a large statistical dataset, obtained by measurements on dedicated FET arrays, we i) propose a methodology to identify and de-convolute the active degradation mechanisms in the device in each point of the device operating bias space, ii) apply this methodology to calculate the operating lifetime in the entire bias space and iii) build a self-heating-aware and thus geometry-independent time-to-failure map.

11:55 AM

## 2A.4 Cap Layer and Multi-Work-Function Tuning Impact on TDDB / BTI in SOI FinFET Devices W. Liu, A. Kerber, F. Guarin and C. Ortolland, GLOBALFOUNDRIES

In this work, we report comprehensive characterization and modeling of time-dependent dielectric breakdown (TDDB) and bias temperature instability (BTI) with multi-work function tuning and a cap layer above high-k in a leading edge SOI FINFET technology.

#### Session 2B - SiC Reliability and Devices

Session Chairs: Aivars Lelis, US Army Research Labs, Matteo Meneghini, University of Padova Tuesday, March 13

10:35 AM - Session Introduction

10:40 AM

#### 2B.1 The Effects of Radiation on the Terrestrial Operation of SiC MOSFETs

B. Akturk, CoolCad

11:05 AM

#### 2B.2 Reliability Studies of SiC Vertical Power MOSFETs (Invited)

D. J. Lichtenwalner, Wolfspeed

11:30 AM

#### 2B.3 SiC Power MOSFET Gate Oxide Breakdown Reliability - Current Status (Invited)

C. Cheung, NIST

11:55 AM

#### 2B.4 Defects Affecting SiC Power Device Reliability (Invited)

R. Stahlbush, NRL

#### Session 2C - ESD/Latchup

Session Chairs: *Michael Khazhinsky, SI Labs, Gianluca Boselli, Texas Instruments* Tuesday, March 13

10:35 AM - Session Introduction

10:40 AM

#### 2C.1 System level ESD and its Implications on I/O Protection (Invited)

David Pommerenke, Missouri University of Science and Technology

11:05 AM

#### 2C.2 Stochastic Modeling of Air Electrostatic Discharge Parameters

Y. Xiu, S. Sagan\*, A. Battini, X. Ma and E. Rosenbaum, University of Illinois, \*Now with IBM

Stochastic modeling is applied to predict the probability distribution of waveform features during air discharges. The variation in these features, even with an unvarying test condition, contributes to the probabilistic nature of soft failures. An automated air discharge tester enables the collection of sufficient data for statistical modeling.

11:30 AM

## 2C.3 An Integral Injector-Victim Current Transfer Model for Latchup Design Rule Optimization G.Quax, T. Smedes, NXP Semiconductors

In this work, we present two models which can be used to optimize latchup design rules. The first model describes the injector-victim current transfer during negative current stresses. It includes all relevant geometrical parameters of the injector, victim, and guardring. The second model describes the trigger current of a parasitic pnp bipolar during external latchup. Both models are combined to determine accurate measures for the required well-tap distance in n-wells near injectors.

11:55 AM

#### 2C.4 Latchup Challenges in FinFET Technologies (Invited)

Krzysztof Domanski, Intel

#### Session 3A - FEOL / MOL / BEOL Breakdown

Session Chairs: Nagarajan Raghavan, Singapore University of Technology and Design, Andrew Kim, IBM Tuesday, March 13

10:35 AM - Session Introduction

#### 1:40 PM

#### 3A.1 Insights into Metal Drift Induced Failure in MOL and BEOL

C. Wu, O. Varela Pedreira, A. Leśniewska, Y. Li, I. Ciofi, Zs. Tőkei, and K. Croes, imec

Co and Cu drift induced degradation were investigated in SiO2. The failure mechanism of building-up metal in dielectrics is attributed to local metal filament nucleation and growth. Metal filament growth limits the failure times at high fields, while metal filament nucleation is more dominant at low fields. The competition between these two mechanisms and intrinsic dielectric degradation makes the collection of TTF in a wide field and temperature test window inevitable for reliable lifetime predictions.

#### 2:05 PM

## 3A.2 Time-Dependent Dielectric Breakdown Statistics in SiO<sub>2</sub> and HfO<sub>2</sub> Dielectrics: Insights from a Multi-scale Modeling Approach

A. Padovani and L. Larcher, Università di Modena e Reggio Emilia

We use physics-based breakdown simulations to investigate the time dependent dielectric breakdown (TDDB) distributions of SiO2 and HfO2 stacks. We show that the low and thickness independent TDDB Weibull slope measured in HfO2 is originated by their intrinsic defect density and the spatially correlated defect generation process. We also demonstrate that the double slope observed in TDDB distributions of IL-HfO2 dielectric stacks is related to the stochastic nature of the bond-breakage process.

#### 2:30 PM

## 3A.3 Elapsed-Time Statistics of Successive Breakdown in the Presence of Variability for Dielectric Breakdown and RRAM applications

E.Y. Wu, A. Kim, B. Li, and J. H. Stathis, IBM Co.

Due to the competition of multiple spots (filaments) culminating in final hard breakdown in very long wires, it is imperative to develop a comprehensive methodology to correctly incorporate this post-BD margin in technology qualification. In filamentary RRAM operation, elapsed-time statistics affects multi-level switching with multiple filaments and the endurance-related lifetime. In this work, we develop a comprehensive methodology for elapsed time statistics of successive breakdown for dielectric breakdown and RRAM applications.

#### 2:55 PM

#### 3A.4 Study on Mechanism of Thermal Curing in Ultra-thin Gate Dielectrics

Y. Mitani, Y. Higashi and Y. Nakasaki, Toshiba Corporation

In order to realize the sustainable devices, thermal curing by self-heating are attracting attention recently. In order to understand the progression of the recovery by heating, in this paper, the thermal curing of the deteriorations at both SiO2 interfaces was investigated in PFETs and NFETs. As results, the damage in PFETs can be recovered even by low temperature curing, but in the case of NFETs, the damage at SiO2/Si interface is hard to be recovered.

3:20 PM

#### 3A.5 New Methodology for Modelling MOL TDDB

P. Roussel, A. Chasin, S. Demuynck, N. Horiguchi, D. Linten and A. Mocuta, imec

We report a novel time-dependent dielectric breakdown (TDDB) lifetime model which accounts for the impact of different sources of variability. We prove that the Weibull and Log¬Normal distributions normally used for FEOL and BEOL TDDB lifetime predictions respectively are not adequate for MOL TDDB analysis. Due to the many sources of variability, only a convolution of Weibull and LogNormal distributions can reconcile the intrinsic break¬down mechanism with the extra variability.

#### Session 3B – FOCUS SESSION: WBG Reliability Synergies and Standardization

Session Chairs: Sandeep Bahl, Texas Instruments, Matteo Meneghini, University of Padova Tuesday, March 13

10:35 AM - Session Introduction

1:40 PM

3B.1 Brief History of JEDEC Qualification Standards for Silicon Technology and Their Applicability to WBG Semiconductors (Invited)

J. McPherson, Consultant

2:05 PM

3B.2 **Physical Failure Analysis Methods for Wide Band Gap Semiconductor Devices (Invited)** *A. Graff, Fraunhofer*

2:30 PM

3B.3 Challenges to Realize Highly Reliable SiC Power Device - From the Current Status and Issues of SiC Wafer (Invited)

J. Senzaki, AIST

2:55 PM

3B.4 Evaluation Methodology for Current Collapse Phenomena of GaN HEMTs (Invited)

T. Sugiyama, Toshiba Corp.

3:20 PM

3B.5 Understanding and Modeling Transient Threshold Instabilities in SiC MOSFETs (Invited) H. Reisinger, Infineon

#### Session 3C - System Reliability

Session Chairs: Guneet Sethi, Amazon Lab 135, Rob Kwasnick, Intel Tuesday, March 13

1:35 PM - Session Introduction

#### 1:40 PM

3C.1 Managing Electrical Reliability in Consumer Systems for Improved Energy Efficiency V. Huard, S. Mhira\*, A. Barclais, X. Lecocq, F. Raugi, M. Cantournet, and A. Bravaix\* STMicroelectronics, \*ISEN-REER

The paper for first time explains how to run realistic electrical reliability qualification trials at system level. Experimental dataset is fully explained by new hierarchical modeling flow. This combined approach enables further tuning of the aging margin to adapt to system usage in the field. This work paves the way to Static Adaptive Voltage Scaling qualification at system level as well as dynamic modulation of aging margin in the field so to improve energy efficiency.

#### 2:05 PM

3C.2 **COTS Electronics Reliability for Space Applications (Invited)** *Jonny Pellish, NASA*

#### 2:30 PM

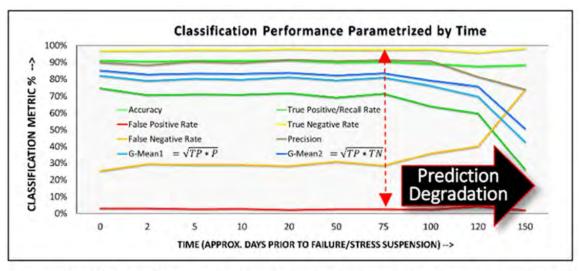

### 3C.3 Machine Learning Based Dynamic Cause Maps for Condition Monitoring and Life Estimation

A. Kale, A. Marathe, A. Kamath, N. Dhar, S. Sellers, Google

Estimating failure modes and life of electronic sub-component in field environment is challenging because of factors such as dynamic field environment, component interactions and errors and variability in operating characteristics. This paper addresses these challenge by developing dynamic cause maps using physics based models, field data and machine learning algorithms.

#### 2:55 PM

#### 3C.4 Exascale Fault Tolerance Challenge and Approaches (Invited)

Cameron McNairy, Intel

#### 3:20 PM

#### 3C.5 Airplane Systems Design for Reliability & Quality (Invited)

Anapathur Ramesh, Boeing

#### 4:10 PM

## 3C.6 Machine-Learned Assessment and Prediction of Robust Solid-State Storage System Reliability Physics

J. Sarkar, C. Peterson, A. Sanayei, Western Digital Corporation

Reliability physics of complex fault-tolerant memory sub-system of solid-state storage is analyzed leveraging Machine Learning, enabling successful inferential and predictive SSD system reliability assessments in a pro-active manner. While being illustrative of applying Machine Learning to complex system reliability, this paper also discusses the first published method (known to the authors) for assessing individual SSD reliability under throughput acceleration.

4:35 AM

### 3C.7 Statistical Modeling and Reliability Prediction for Transient Luminance Degradation of Flexible OLEDs

H. Kim, H. Shin, J. Park, Y. Choi, J. Park, Technology Reliability, OLED Business Samsung Electronics

We, herein, propose a modified stretched exponential decay (MSED) model in the consideration of transient luminescence decay with respect to intrinsic emissive layer dependent initial luminescence and subsequent degradation over the constant current stress tests. By using the model well fitted to experimental data measured from accelerated stress tests extrapolated to user conditions, we successfully demonstrate that a MSED extracted from statistical modeling enables the precise lifetime prediction with respect to process variation and duty factor in real operation conditions.

5:00 PM

#### 3C.8 Reliability of MEMS Sensors Through SelfCcalibration (Invited)

A. Lal, Cornell University

#### Session 3D - Product IC Reliability

Session Chairs: *Brian Pedersen, Intel, Pierre Chor-Fung Chia, Cisco* Tuesday, March 13

4:05 PM - Session Introduction

4:10 PM

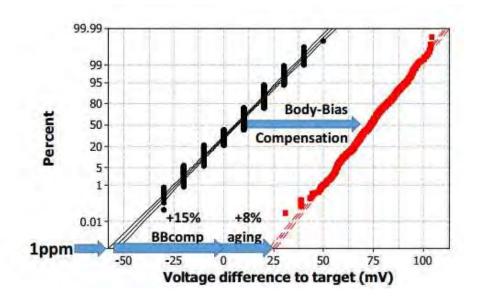

### 3D.1 Resilient Automotive Products Through Process, Temperature, and Aging Compensation Schemes

S. Mhira, V. Huard, D. Arora, P. Flatresse\* and A. Bravaix\*\*, STMicroelectronics, STMicroelectronics, \*SOITEC, \*\*ISEN-REER, IM2NP,

A 32b SoC is designed in 28nm FDSOI to operate for safety-critical applications with joint Process, Temperature and Aging compensation schemes using body-bias. This work demonstrates that up to 74% energy efficiency can be gained by combining Body-Bias Process, Temperature and Aging compensation schemes altogether. This combination of compensation schemes offers the best energy efficiency gain as compared to recent results while guaranteeing high-level of robustness (<1 ppm) and safety for automotive products.

4:35 AM

3D.2 **Fast Chip Aging Prediction by Product-like V**<sub>min</sub> **Drift Characterization on Test Structures** S. E. Liu, G. Y. Chen\*, M. K. Chen\*, D. Yen, W. A. Kuo, C. S. Fu, Y. S. Tsai\*, M. Z. Lin, Y. H. Fang, M. J. Lin, MediaTek Inc., \* Taiwan Semiconductor Manufacturing Company, Ltd.

We develop a novel product-like characterization methodology to predict chip aging rapidly. To assure reliability, an aging voltage guard band is usually collected by HTOL and implemented to a chip's voltage setting. We proposed a method to mimic product-like characterization on test structures to evaluate Vmin shift. Then, the correlation was established between test structure measurements and chip-level Vmin shift analysis. Therefore, product aging guard-band can be assessed rapidly with process and use condition changes.

5:00 PM

## 3D.3 Reliability Characterization of Advanced CMOS Image Sensor (CIS) with 3D Stack and Inpixel DTI

Y. Ji, J. Kim, J. Kim, M. Lee, J. Noh, T. Jeong, J. Shin, J. Kim, Y. Heo, U. Cho, H. Sagong, J. Park, Y. Choo, G. Do, H. Kang, E. Choi, D. Sun, C. Kang, S. Shin, and S. Pae, Samsung Electronics

Due to the advancement of CMOS image sensors, camera module on the mobile platform has paved way for very high quality photos and video shooting capability. In order to improve picture quality, the CIS technology has been also scaling aggressively to provide more Mega-Pixels but it also must be less susceptible and immune to noise sources, particle, and highly reliable. In this report, we'll discuss the reliability characterization done on the 3D stack sensor.

#### Session 3E - ESD/Latchup

Session Chairs: *Michael Khazhinsky, SI Labs, Gianluca Boselli, Texas Instruments* Tuesday, March 13

4:05 PM - Session Introduction

4:10 PM

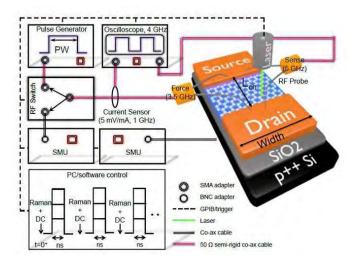

3E.1 **Defect-Assisted Safe Operating Area Limits and High Current Failure in Graphene FETs** N. K. Kranthi, A. Mishra, A. Meersha, H. B. Variar and M. Shrivastava, Indian Institute of Science

In this work, a unique measurement setup, involving integration of transmission line pulse tester with Raman spectrometer, is used to investigate the pulsed safe operating area (SOA) boundary of graphene field effect transistors (GFETs). Physical insight into various SOA boundaries is given. Unique defect-assisted degradation in channel and its correlation with the carrier transport and failure is revealed. The SOA and power to fail dependency on carrier concentration and nature of carrier transport is addressed.

4:35 PM

## 3E.2 On the ESD Behavior of a-Si:H based Thin-Film Transistors: Physical Insights, Design and Technological Implications

R. Sinha, P. Bhattacharya, S. Sambandan and M. Shrivastava, Indian Institute of Science

In this work, we present detailed physical and technological insights into the ESD behavior of a-Si:H TFTs. Pre-Breakdown degradation is investigated. Device failure and effect of various parameters on failure is investigated. Effect of Channel dimensions on failure mechanism is thoroughly explored. For the first time, ESD behavior of a-Si:H based Gated diodes and Resistors is reported. Detailed Investigation on Drain Underlap devices and their possible usage as I/O protection device is discussed.

5:00 PM

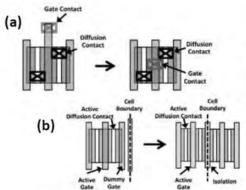

## 3E.3 Contact and Junction Engineering in Bulk FinFET Technology for Improved ESD/Latch-up Performance with Design Trade-offs and Its Implications on Hot Carrier Reliability

M. Paul, B. Sampath Kumar, H. Gossner\* and M. Shrivastava, Indian Institute of Science, \*Intel Deutschland

Role of contact and junction engineering to improve ESD and Latch-up robustness while addressing its's implications on hot carrier reliability is discussed. Contact and junction engineering boosts ESD and latch-up robustness, however can adversely affect the HCI reliability, which has been explored in this work

keeping all ESD/Latch-up design parameters in mind. This has allowed us to derive technology guidelines for maximizing overall reliability behavior. Based on these guidelines, a hybrid contact/junction technology is proposed.

#### Session 4A - FEOL / MOL / BEOL Breakdown

Session Chairs: Nagarajan Raghavan, Singapore University of Technology and Design, Andrew Kim, IBM Wednesday, March 14

8:00 AM - Session Introduction

#### 8:05 AM

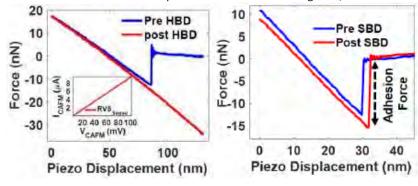

#### 4A.1 Mechanism of Soft and Hard Breakdown in Hexagonal Boron Nitride 2D Dielectrics

A. Ranjan, N. Raghavan, S.J. O'Shea\*, S. Mei, M. Bosman\*, K. Shubhakar and K.L. Pey, Singapore University of Technology and Design (SUTD), A\*STAR

In this study, we investigate the physical mechanism of soft and hard breakdown using conductive atomic force microscope (CAFM) as a nanoscale spectroscopy tool on blanket h-BN films with tox = 5 nm. The soft breakdown (SBD) regime involves percolation path formation with boron vacancies while the hard breakdown (HBD) regime shows nano-pitting that involves removal of h-BN layers and formation of a metallic contact due to CAFM tip adhesion with the Cu substrate.

#### 8:30 AM

### 4A.2 The Physical Mechanism Investigation of Off-State Drain Bias TDDB and its Implication in Advance HK/MG FinFETs

I. K. Chen, S. C. Chen, S. Mukhopadhyay, D. S. Huang, J. H. Lee, Y. S. Tsai, R. Lu, J. He, Taiwan Semiconductor Manufacturing Company, Ltd.

This work presents a systematic study to understand the off-state drain bias TDDB mechanism, especially for the short channel devices in advanced FinEFT technologies. With additional process optimization such as source/drain proximity push, the sub-threshold leakage current increases, which dominates the off-state TDDB resulting in worse lifetime during practical circuit stress conditions. Impact of body bias on sub-threshold current is also studied with detailed mechanism.

#### 8:55 AM

## 4A.3 AC TDDB Extensive Study for an Enlargement of Its Impact and Benefit on Circuit Lifetime Assessment

M. Rafik A.P. Nguyen\*, X. Garros\*, M. Arabi, X. Federspiel, C. Diouf, ST Microelectronics, \*CEA-Leti

Abstract – With technology scaling and hardening of operating conditions requirements, Time Dependent Dielectric Breakdown (TDDB) remains a major reliability concern. In this paper we show that considering AC rather than DC TDDB would be a promising way to generate margin on lifetime assessment and also to lower the predicted impact of the breakdown on circuit functionality.

9:20 AM

#### 4A.4 A Systematic Study of Gate Dielectric TDDB in FinFET Technology

H. Kim, M. Jin, H. Sagong, J. Kim, U. Jung, M. Choi, J. Park, S. Shin and S. Pae, Samsung Electronics

TDDB may have been qualified with only considering operating Ninv and Pinv, but it is necessary to consider all modes including the accumulation mode & off-state mode as well for correctly assessing product level gate oxide dppms and remove conservatism. This along with AC stresses further enables the reliability margin, otherwise, cannot be fully explained generally large gap observed between wafer-level DC based TDDB and product level HTOL, extending technology Vmax headroom without reliability tradeoffs.

9:45 AM

## 4A.5 Successive Breakdown Mode of Time-Dependent Dielectric Breakdown for Cu Interconnect and Lifetime Enhancement under Dynamic Bias Stress

S.K. Lee, K.T. Jang, S.M. Yi and Y.C. Joo, Seoul National University

In gate dielectrics, successive breakdown (BD) was caused by randomly generated bond breakages of the dielectrics. In inter-metal dielectrics, we confirmed that successive BD occurred by the formation of metallic filaments for the first time. The filaments of the successive BD are consisted of Cu atoms mediating bond breakages. Moreover, TDDB lifetime was improved under bipolar stress compared to DC and unipolar stresses due to Cu atom to ion conversion and formation of misaligned filaments.

#### Session 4B - GaN-based devices reliability

Session Chairs: Sandeep Bahl, Texas Instruments, Matteo Meneghini, University of Padova Wednesday, March 14

8:00 AM - Session Introduction

8:05 AM

#### 4B.1 Degradation of Vertical GaN FETs Under Gate and Drain Stress

M. Ruzzarin, M. Meneghini, C. De Santi, M. Sun\*, T. Palacios\*, G. Meneghesso, and E. Zanoni, University of Padova, \*Massachusetts Institute of Technology

We report the analysis of degradation of GaN VFETs under gate and drain stress. High gate bias induces the injection of electrons from the channel towards the gate dielectric (positive Vth shift) and the detrapping of electrons from the gate insulator to the gate metal (increase in SS). The results of drain step stress reveal that the devices are stable up to VD=280 V, with no significant change in device characteristics.

8:30 AM

#### 4B.2 A Novel Insight of pBTI Degradation in GaN-on-Si E-mode MOSc-HEMT

W. Vandendaele, X. Garros, T. Lorin, E. Morvan, A. Torres, R. Escoffier, MA Jaud, M. Plissonnier, F. Gaillard, CEA-Leti

GaN-on-Si HEMT technology is now considered as a serious candidate for medium power applications (650V rated). Vth instabilities are a major concern to increase lifetime of these power transistors. Advanced E-mode MOSc-HEMT (MOS-channel-HEMT) configuration has been recently introduced and studied under harsh gate conditions. In this paper we present for the first time a comparison between AC and DC stress combined with ultra-fast pBTI measurements (< 10µs) on GaN-on-Si E-mode MOSc-HEMTs.

8:55 AM

#### 4B.3 Reliability Issues of GaN Commercialization (Invited)

U. Mishra, University of California, Santa Barbara

9:20 AM

## 4B.4 Comprehensive Study into Underlying Mechanisms of Anomalous Gate Leakage Degradation in GaN HEMTs

K. Mukherjee, F. Darracq, A. Curutchet, N. Malbert and N. Labat, IMS Lab, University of Bordeaux

This work investigates fundamental mechanisms governing an atypical parasitic gate leakage characteristic observed in DC forward gate behavior of Schottky gate GAN HEMTs after aging tests. DC measurements are performed to ascertain its long term impact. Detailed TCAD simulation study, for the first time to ourknowledge, reproduces this anomaly through donor state induced surface leakage and trap assisted tunneling across the AlGaN barrier. A proposed hypothesis addresses the unpredictable evolution of this effect.

9:45 AM

#### 4B.5 On the Origin of the Leakage Current of p-Gate AlGaN/GaN HEMTs

A. Stockman, E. Canato\*\*, M. Meneghini\*\*, G. Meneghesso\*\*, E. Zanoni\*\*, P. Moens and B. Bakeroot\*

ON Semiconductor, \*CMST imec / Ghent University, \*\*University of Padova

Temperature dependent DC and double pulse measurements are performed on p-GaN gated AlGaN/GaN enhancement mode power transistors. Devices with improved Schottky metal barrier and p-GaN sidewall passivation are studied. It is shown that both processes reduce the reverse and forward gate leakage current significantly. Under double pulsed testing, a positive threshold shift at high forward gate voltage is induced, which is explained by electron trapping in the barrier.

#### Session 4C - Soft Error

Session Chairs: Marta Bagatin, University of Padova, Nihaar Mahatme, NXP Semiconductors Wednesday, March 14

8:00 AM - Session Introduction

8:05 AM

### 4C.1 Scaling Trends and Bias Dependence of the Soft Error Rate of 16 nm and 7 nm FinFET SRAMs

B. Narasimham, S. Gupta, D. Reed, J. K. Wang, N. Hendrickson and H. Taufique, Broadcom Ltd.

SRAM SER measurements across technology nodes indicate that while scaling from planar to the first FinFET process provided a large reduction in per-bit SER, the subsequent scaling within FinFET process nodes results in SER reduction comparable to per-bit cell area reduction. Extensive SER measurements over a range of voltages show a strong exponential increase in the SER of FinFET processes with reduction in bias, compared to a linear bias dependence for the planar process.

8:30 AM

#### 4C.2 Soft Errors in 7nm FinFET SRAMs with Integrated Fan-out Packaging

Y. Pin Fang and A.S. Oates, Taiwan Semiconductor Manufacturing Company

The susceptibility of alpha induced soft error rate (SER) is dominated by extrinsic alpha sources in packaging such as lead-bearing solder, and bumping materials. Using wafer-level integrated fan-out (InFO) packaging technology, alpha particles emitted from extrinsic packaging materials can be blocked by redistribution layers (RDL) in InFO packaging, leaving the SER susceptibility due to intrinsic alpha sources in Si process. With technology scaling, voltage dependent SER due to intrinsic alpha particles as well as high-energy neutrons is significantly reduced in 7nm SRAM.

#### 8:55 AM

## 4C.3 Threshold Ion Parameters of Line-Type Soft-Errors in Biased Thin-BOX SOI SRAMs: Difference between Sensitivities to Terrestrial and Space Radiation

C. Chung, D. Kobayashi, and K. Hirose, University of Tokyo and Institute of Space and Astronautical Science

Thin-BOX SOI technology is drawing attention for its low soft error sensitivity. Terrestrial radiation tests already demonstrated its further reduction under a back-bias condition. However, recent heavy ion tests with SRAMs exhibited the opposite result, a 100-fold increase accompanying 10-bits-long line-type multicell upsets, when they were biased. A metal bridge model suggests that this difference in response to the back-bias conditioning stems from the difference in ion parameters such as range and linear energy transfer.

#### 9:20 AM

# 4C.4 Impact of Supply Voltage and Particle LET on the Soft Error Rate of Logic Circuits H. Jiang, H. Zhang, R. C. Harrington, J. A. Maharrey, J. S. Kauppila, L. W. Massengill, and B. L. Bhuva, Vanderbilt University

Heavy-ion irradiations of 14/16-nm node bulk FinFET combinational logic circuits under different supply voltage and frequency are investigated. Results indicate that particle LET strongly affects logic soft-error rate (SER). Singe-event transient (SET) experimental data and models for logic SER are used to explain the differences in SER for low-LET particles and high-LET particles.

#### 9:45 AM

## 4C.5 Evaluation of the System-Level SER Performance of Gigabit Ethernet Transceiver Devices B. Narasimham, T. Wu, J. K. Wang, B. Conway, Broadcom Ltd.

System-level SER measurements were conducted on two Gigabit Ethernet transceiver devices designed in 28-nm CMOS process to evaluate the true impact of soft error upsets. Measurement results are compared with the system SER estimates based on test chip data for memory and flip-flop SER. Results indicate that most SEUs cause packet errors which are recoverable while the SER for more severe link-drop type events is significantly lower than estimates.

#### Session 4D - FOCUS SESSION: 3D/2.5D/Packaging/MEMS

Session Chairs: Kothandaraman Chandrasekara, IBM, Sudarshan Rangaraj, Amazon Lab 126 Wednesday, March 14

10:30 AM - Session Introduction

10:35 AM

## 4D.1 High-Density Fan-Out Technology for Advanced SiP and Heterogeneous Integration (Invited)

K. Lee. Amkor

11:00 AM

#### 4D.2 Intra- and Inter-Chip Electrical Interconnection Formation by DSA (Invited)

M. Mariappan, Tohuku University

11:25 AM

#### 4D.3 Stress Mitigation of 3D-packaging Induced Stresses (Invited)

C. Croes. imec

11:50 AM

## **4D.4** Fine Pitch **3D** Interconnections with Hybrid Bonding Technology: Process Robustness and Reliability Results (Invited)

L. Arnaud, CEA /LETI

12:15 PM

#### 4D.5 Reliability Concerns for Advanced Packaging (Invited)

S. Iyer, UCLA

#### Session 4E - GaN-based devices robustness

Session Chairs: Sandeep Bahl, Texas Instruments, Matteo Meneghini, University of Padova Wednesday, March 14

10:30 AM - Session Introduction

10:35 AM

#### 4E.1 p-GaN gate reliability including short-circuit robustness (Invited)

A. Castelazzi, University of Nottigham

11:00 AM

## 4E.2 Lifetime evaluation for Hybrid-Drain-embedded Gate Injection Transistor (HD-GIT) under practical switching operations

A. Ikoshi, M. Toki, H. Yamagiwa, D. Arisawa, M. Hikita, K. Suzuki, M. Yanagihara, Y. Uemoto, K. Tanaka and T. Ueda, Panasonic Corporation

The GaN transistors' reliability under continuous switching operation is a very important topic. We perform dynamic high-temperature operating lifetime (D-HTOL) test on Hybrid-Drain-embedded Gate Injection Transistors (HD-GITs) with varying input voltage, switching current and temperature to extract their acceleration factors on the switching lifetime of HD-GITs. The obtained factors are employed to estimate

the lifetime when they are used for a totem-pole power factor correction circuit to conclude that the estimated lifetime is sufficiently long.

#### 11:25 AM

4E.3 **Safe Operating Area (SOA) Reliability of Polarization Super Junction (PSJ) GaN FETs**B. Shankar, A. Soni, S.D. Gupta, S. Yagi\*, H. Kawai\*, V. Unni\*\*, A.Nakajima\*\*, M. Shrivastava, and E. M. Sankara Narayanan\*\*, Indian Institute of Science, \*Powdec K.K., \*\*University of Sheffield

This work reports Safe Operating Area assessment and degradation physics in Polarization Super Junction (PSJ) based GaN FETs made in Silicon and Sapphire substrates under high voltage and high current injection conditions. Impact of device design parameters on SOA, associated trap assisted device degradation and thermal failure are studied. Correlation between polarization super junction length and failure threshold is discovered, beside power and field dependence of SOA boundary.

#### 11:50 AM

4E.4 On the Trap Assisted Stress Induced Safe Operating Area Limits of AlGaN/GaN HEMTs B. Shankar, A. Soni, S. Dutta Gupta, R. Sengupta, H. Khand, N. Mohan, S. Raghavan and M. Shrivastava, Indian Institute of Science

This experimental study reports a systematic investigation of Safe Operating Area limits in AlGaN/GaN HEMT using sub-us pulse characterization with on-the-fly Raman and CV characterization to probe defect and stress evolution across the device. Influence of a recess depth on SOA boundary is analyzed. Post failure analysis corroborates well with the failure physics unveiled in this work.

#### 12:15 PM

## 4E.5 Reliable and Damage-Resistant Optics and Detectors for X-Ray Free-electron Lasers (Invited)

S. Hau-Riege, Lawrence Livermore National Labs

X-ray free-electron lasers (XFELs) are revolutionizing the physical and life sciences. The sweeping recent success of XFELs can be attributed to their extreme output characteristics: XFELs deliver x-ray photon pulses that are more than nine orders of magnitude brighter than any previous laboratory light source, like synchrotrons. Such extreme radiation poses a particular challenge for the short- and long-term reliability of x-ray optics and detectors which are required to steer, condition, and diagnose individual x-ray pulses. In this presentation, we will discuss how we overcame the challenges of designing damage-resistant optics and detectors without ever having had access to such radiation.

#### Session 4F - Metallization Reliability

Session Chairs: *Gavin Hall, ON Semi, Zsolt Tokei, IMEC* Wednesday, March 14

10:30 AM - Session Introduction

10:35 AM

4F.1 Next Generation Interconnect Reliability Metallization Integration (Invited)  $\textit{C-K}\ \textit{Hu}, \textit{IBM}$

#### 11:00 AM

## 4F.2 Electromigration-Induced Backflow Stresses in Cu(Mn) Interconnects Analyzed Based on High Statistical Sampling

M. Kraatz, C. Sander, A. Clausner, M. Hauschildt\*, M. Gall, and E. Zschech Fraunhofer Institute for Ceramic Technologies and Systems IKTS, \*GLOBALFOUNDRIES LLC & Co. KG,

Using an alternate Wheatstone bridge setup, sampling over a total of 800 Cu(Mn) interconnects resulted in very smooth resistance vs. time curves during the electromigration process. The test temperature was 350 °C and several current densities ranging from 13 to 17 mA/ $\mu$ m² were applied. Using the averaged resistance curves, linear drift portions were extracted and saturation resistances were extrapolated. The data was further analyzed to obtain a critical Blech product of (510 ± 110) mA/ $\mu$ m.

#### 11:25 AM

#### 4F.3 Electromigration Characteristics of Power Grid Like Strcutures

B. Li, A. Ki, P. McLaughlin, B. Linder and C. Christiansen, IBM Systems

Setting appropriate EM limit becomes more and more critical for the leading edge technologies, especially for on-chip power grid. This paper presents EM characteristics of power grid like structures. It demonstrates that the EM reliability is much enhanced from the power grid design environment comparing to the traditional single link EM structures. Discussions are made on the contributing factors to this EM reliability enhancement and how they should be utilized.

#### 11:50 AM

#### 4F.4 Effect of Metal Line Width on Electromigration of BEOL Cu Interconnects

S. Choi, C. Christiansen, L. Cao, J. Zhang, R. Filippi Jr., T. Shen, K. B. Yeap, S. Ogden, H. Zhang, B. Fu, P. Justison, GLOBALFOUNDRIES

Electromigration reliability of BEOL Cu interconnects with various metal line widths and via sizes has been studied. EM lifetime improves from minimum width to three times the minimum width, and then saturates. The proposed mechanism for EM lifetime improvement is larger grains in wider lines leading to a reduction in grain boundary diffusion. Cu grain size and Cu drift velocity were correlated to the EM lifetime behavior.

#### 12:15 PM

#### 4F.5 Protective Nanometer Films for Reliable Cu-Cu Connections (Invited)

T. Berthold, G. Benstetter, W. Frammelsberger, M. Bogner, R. Rodríguez, M. Nafría, Autonomous University of Barcelona, and Deggendorf Institute of Technology

#### Session 5A - Transistors: Models and Characterization

Session Chairs: *Steve Ramey, Intel, Tibor Grasser, TUWien* Wednesday, March 14

2:15 PM - Session Introduction

#### 2:20 PM

## 5A.1 Hot Electron and Hot Hole Induced Degradation of SiGe p-FinFETs Studied by Degradation Maps in the Entire Bias Space

J. Franco, B. Kaczer, A. Chasin, E. Bury, D. Linten, imec

We study hot carrier degradation in Si<sub>0.75</sub>Ge<sub>0.25</sub> p-FinFETs by measuring degradation maps in the entire bias space, and compare with Si counterparts. Hot carrier effects are enhanced in SiGe due to larger hole mean free path, and enhanced generation of secondary electrons in the reduced bandgap semiconductor. Both hole and electron injections are observed, partially compensating at some stress biases. Even at logic operating voltages, off-state stress increases the channel leakage due to hot-electron-induced punch-through.

#### 2:45 PM

5A.2 Role of Electron and Hole Trapping in Degradation and Breakdown of Oxide Films (Invited)

A. Shluger, University College, London

#### 3:10 PM

### 5A.3 Impact of Slow and Fast Oxide Traps on In<sub>0.53</sub>Ga<sub>0.47</sub> As Device Operation Studied Using CET aps

V. Putcha<sup>(1,2)</sup>, J. Franco<sup>(2)</sup>, A. Vais<sup>(2)</sup>, B. Kaczer<sup>(2)</sup>, S. Sioncke<sup>(2)</sup>, D. Linten<sup>(2)</sup> and G. Groeseneken<sup>(1,2)</sup> (1) ESAT department, KU Leuven, (2) IMEC

Kinetics of charge trapping in the InGaAs/Al2O3/HfO2 gate-stack is studied using CET maps. A first defect population with relatively higher capture and emission energy barriers is found to affect the long term reliability of the device, while a second population with relatively smaller capture and emission energy barriers affects the device stability under high frequency operation. We conclude, it is essential to study both defect populations for accurately estimating device lifetime under different operating applications.

#### 3:55 PM

## 5A.4 PBTI in InGaAs MOS Capacitors with Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/TiN gate stacks: Interface-state Generation

E. Cartier, M. M. Frank, T. Ando, J. Rozen and V. Narayanan, IBM Research Division, T.J. Watson Research Center

Using devices with well passivated interfaces and reduced electron trapping it is demonstrated that significant interface-state generation occurs during PBTI stress in InGaAs MOS capacitors with  $Al_2O_3/HfO_2/TiN$  gate stacks. These observations on capacitors imply that the impact of interface-state generation on mobility and subthreshold degradation need to be monitored in III-V nFET once the electron trapping is brought under control.

#### 4:20 PM

## 5A.5 Reliability of Next-Generation Field-Effect Transistors with Transition Metal Dichalcogenides

Y.Y. Illarionov\*, A.J. Molina Mendoza, M. Waltl, T. Knobloch, M.M. Furchi, T. Mueller and T. Grasser, TU Wien, \*also with Ioffe Physical-Technical Institute

We perform a detailed reliability study of MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub> and WS<sub>2</sub> FETs fabricated on the same SiO<sub>2</sub>/Si substrate and compare the hysteresis and BTI dynamics for these devices. Our results show that the observed differences can be partially explained by the alignment of the band edges of the 2D semiconductors with the defect bands in SiO<sub>2</sub>. As such, our study provides strong fundamental insights into the understanding of the reliability of these new technologies.

4:45 PM

### 5A.6 Hot Carrier Degradation, TDDB, and 1/f Noise in Poly-Si Tri-gate Nanowire Transistor Y. Yoshimura, K. Ota and M. Saitoh, Toshiba Corporation

We study various reliabilities in poly-Si nanowire transistors. Unique hot carrier degradation characteristics are found at low stress gate voltage where degradation was reduced due to suppressed drain avalanche hot carrier by grain boundary. Time dependent dielectric breakdown shows enhanced breakdown probability at nanowire corner similar to SOI nanowire transistors, while breakdown-time distributions is related to randomly oriented grain surface. 1/f noise shows conventional size dependence, while noise amplitude is related to grain size.

#### Session 5B - 3D/2.5D/Packaging/MEMS

Session Chairs: Kothandaraman Chandrasekara, IBM, Sudarshan Rangaraj, Amazon Lab 126 Wednesday, March 14

2:15 PM - Session Introduction

2:20 PM

#### 5B.1 Analysis of 28 nm SRAM Cell Stability Under Mechanical Load Applied by Nanoindentation

A. Clausner<sup>1</sup>, G. Kurz\*, M. Otto\*, J. Paul\*, K.-U. Gierin\*\*, J. Warmuth\*\*, R. Jancke\*\*, A. Aal#, M. Gal, and E. Zschech, Fraunhofer Institute for Ceramic Technologies and Systems IKTS, \*GLOBALFOUNDRIES LLC & Co. KG, \*\*Fraunhofer Institute for Integrated Circuits IIS, Engineering of Adaptive Systems EAS, #Volkswagen AG

28 nm high-k metal gate CMOS SRAM circuits were subjected to controlled mechanical load by nanoindentation. This enables high stress fields in the vicinity of operational SRAM cells. It was found that the loading leads to an increase of the bit cell fail probability around the nanoindentation point. The results attained here provide a quantitative estimate about the influence of package-related stress on performance and reliability of microelectronic products, shedding light on CPI- and CBI-effects.

2:45 PM

#### 5B.2 Electromigration of multi-solder ball test structures

C. Hau-Riege, H. Xu, Y.-W. Yau, M. Kakade, J. Li, X. Zhang, H. Farr\*, Qualcomm Technologies, Inc., \*Oualitau.

This study investigates the electromigration failure characteristics for wafer-level packaging multi-ball structures with different ball numbers, trace sizes, and current distributions. Unlike single-interconnect structures, the resistance and voltage measurements of multi-ball structures show distinct steps and inflections, corresponding to individual ball fails, which was confirmed through failure analysis. Electromigration performance is greatly enhanced by splitting current amongst balls and by increasing the trace size.

3:10 PM

5B.3 Reliability Challenges in 2.5D Packaging and Embedded Silicon Bridge (Invited)

E. Armagan, Intel

3:55 PM

#### 5B.4 Reliability Challenges on 2.5D/3D Chip Integration - an Overview (Invited)

C. S. Premachandran, GLOBALFOUNDRIES

4:20 PM

#### 5B.5 TSV Process-Induced MOS Reliability Degradation

Y. Li, M. Stucchi, S. Van Huylenbroeck, G. Van Der Plas, G. Beyer, E. Beyne, K. Croes, imec

Process-induced MOS capacitor reliability degradation is investigated for both "via-last" and "via-middle" TSV flows. It is shown that during via-last TSV processing, the MOS capacitor reliability is impacted by both the TSV liner open dry etch and the PVD metal barrier deposition. With a protection PN diode, the MOS reliability degradation can however be prevented. In comparison, the reliability degradation in a via-middle flow, caused by the backside TSV dry-etch reveal process, is negligible.

4:45 PM

#### 5B.6 Device Reliability for CMOS Image Sensors with Backside TSVs

J.P. Gambino, H. Soleimani, I. Rahim, B. Riebeek, L. Sheng, H. Truong, G. Hall, R. Jerome, D. Price, ON Semiconductor

In this study, device reliability is characterized for two different 0.18 um BSI image sensor technologies. We show that for devices with an SiO2 liner over the gates and with SiN backside dielectrics, the backside processing can degrade device reliability (due to hydrogen depassivation) and that backside process optimization is required to achieve acceptable device reliability (to allow effective repassivation during the final hydrogen anneal).

#### Session 5C - Circuit Reliability/Aging

Session Chairs: Chris Kim, University of Minnesota, Georgios Konstadinidis, Google Wednesday, March 14

2:15 PM - Session Introduction

2:20 PM

## 5C.1 Recent Advances in In-situ and In-field Aging Monitoring and Compensation for Integrated Circuits Monitoring and Compensation for Integrated Circuits (Invited)

M. Seok. Columbia University

2:45 PM

#### 5C.2 All-Digital PLL Frequency and Phase Noise Degradation Measurements Using Simple On-Chip Monitoring Circuits

G. Park, \*B. Kim, M. Kim, \*\*V. Reddy, C. H. Kim, University of Minnesota, \*Nanyang Technological University, \*\*Texas Instruments

Using simple on-chip monitoring circuits, we precisely characterized the impact of hot carrier injection and bias temperature instability aging on frequency and phase noise degradation of a 65nm all-digital PLL circuit. Experimental data shows that PLL phase noise degrades with aging even though the output frequency is maintained constant due to the PLL feedback operation. Results show that applying high temperature annealing can recover most of the phase noise degradation.

3:10 PM

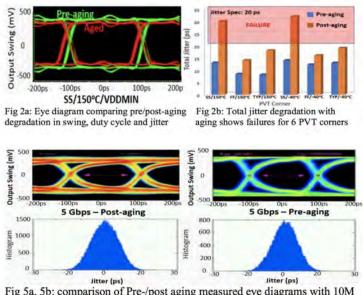

#### Design of Aging Aware 5 Gbps LVDS Transmitter for Automotive Applications 5C.3

S. Jagannathan, K. Abhishek, T. Goyal, N. Mahatme, G. Easwaran, NXP Semiconductors

This work investigates the effect of circuit aging on 5 Gbps LVDS Transmitter (TX) used in automotive SoCs. A sensitivity analysis of sub-blocks is discussed, imulations suggest aging induced minor increase in Vth results in system failure. On-chip aging adaptive capability is achieved using jitter and duty-cycle correction circuity to recover critical TX performance within its specifications. Experiments confirms the efficacy of mitigation techniques, with TX restoring its performance to <5% from its pre-aging values.

3:55 PM

#### 5C.4 Reliability Perspective of Resistive Synaptic Devices on the Neuromorphic System **Performance (Invited)**

S. Yu, Arizona State University