For More Information IEDM Online: irps.org

# **Table of Contents**

| Intro                                | 3       |   |

|--------------------------------------|---------|---|

| Committees                           | 3       |   |

| Topics of Interest                   | 5       |   |

| Program:                             |         |   |

| Keynote Speakers                     | 6       |   |

| Invited Speakers                     | 6       |   |

| Tutorials                            | 7       |   |

| Workshops                            | 8       |   |

| Year in Review                       | 8       |   |

| Highlighted Papers                   | 9       |   |

| Poster Session                       | 9       |   |

| Exhibits & Exhibit Events            | 10      |   |

| Abstracts, Bios for Tutorials, Short | Courses | ደ |

|                                      |         | ر |

| Technical ProgramAp                  | penaix  |   |

#### Intro

For 59 years, IRPS has been the premiere conference for engineers and scientists to present new and original work in the area of microelectronics reliability. Drawing participants from the United States, Europe, Asia, and all other parts of the world, IRPS seeks to understand the reliability of semiconductor devices, integrated circuits, and microelectronic systems through an improved understanding of both the physics of failure as well as the application environment.

IRPS provides numerous opportunities for attendees to increase their knowledge and understanding of all aspects of microelectronics reliability. It is also an outstanding chance to meet and network with reliability colleagues from around the world.

IRPS is Co-Sponsored by IEEE EDS and Reliability Society

# **Digital & Social Media**

• Facebook: @IEEE-IRPS-239965161886

• Twitter: @IEEEIRPS

• LinkedIn: https://www.linkedin.com/groups/2624656/profile

YouTube: @IEEEIRPSInstagram: @ieee\_irps

Weibo: http://weibo.com/u/5500677074

# Committees Executive Committee

#### **General Chair**

Robert Kaplar Sandia rjkapla@sandia.gov

#### **Vice General Chair**

Charles Slayman Cisco Systems cslayman@cisco.com

#### **Technical Program Chair**

Chris Connor Intel chris.connor@intel.com

#### **Finance Chair**

Koji Eriguchi Kyoto University eriguchi.koji.8e@kyoto-u.ac.jp

#### **Arrangements Chair**

Susumu Shuto Toshiba susumu.shuto@toshiba.co.jp

# Audio Visual / Presentations Chair

Barry Linder IBM bplinder@us.ibm.com

#### **Communications Chair**

Georgios Konstadinidis Google gkonstad@google.com

#### **Publications Chair**

Marta Bagatin University of Padova marta.bagatin@dei.unipd.it

#### **Publicity Chair**

Ben Kaczer IMEC kaczer@imec.be

#### **Registration Chair**

Tibor Grasser TU Wien arasser@iue.tuwien.ac.at

#### **Tutorials Chair**

Jason Ryan NIST jason.ryan@nist.gov

#### **Workshops Chair**

Christine Hau-Riege Qualcomm chaurieg@qti.qualcomm.com

#### **Exhibits Chair**

Patick Justison

Global Foundries

patrick.justison@globalfoundries.com

#### Secretary

Shireen Warnock MIT Shireen.Warnock@ll.mit.edu

# Past General Chair and BOD Chair

Gaudenzio Meneghesso University of Padova gauss@dei.unipd.it

#### **Conference Manager**

Lisa Boyd IEEE MCE IRPSplanners@ieee.org

# Circuit Reliability and Aging

Chair Florian Cacho florian.cacho@st.com

Vice-Chair Mingoo Seok ms4415@columbia.edu

# **Emerging Memory** Reliability

Chair Tetsuo Endoh tetsuo.endoh@cies.tohoku.ac.jp

Vice-Chair Shimeng Yu shimeng.yu@ece.gatech.edu

### **ESD and Latchup**

Chair Mototsugu Okushima mototsugu.okushima.vx@renesas.com

Vice-Chair Michael Stockinger m.stockinger@nxp.com

# **Failure Analysis**

Chair Brendan Foran brendan.j.foran@aero.org

Vice-Chair Christian Schmidt christians@nvidia.com

# **Gate/MOL Dielectrics**

Chair Francesco Maria Puglisi francescomaria.puglisi@unimore.it

Vice Chair Andrea Padovani andrea\_padovani@amat.com

### IC Product Reliability

Chair Richard (Shiguo) Rao rrao@inphi.com

Vice chair Sandhya Chandrashekhar Sandhya.Chandrashekhar@cypress.com

# **Memory Reliability**

Chair Jiezhi Chen chen.jiezhi@sdu.edu.cn

Vice-Chair Shu-jen Lee Shu-jen.lee@intel.com

# Metallization/BEOL Reliability

Chair Rahim Kasim rahim.kasim@intel.com

Vice-Chair Ming-Hsien Lin mhlinza@tsmc.com

### Neuromorphic Computing Reliability

Chair Kin Leong Pey peykinleong@sutd.edu.sg

Vice-Chair Tuo-Hung Hou thhou@mail. nctu.edu.tw

# Packaging and 2.5/3D Assembly

Chair CS (Prem) Premachandran premachandran.cs@globalfoundries.com

Vice-Chair Preeti Chauhan chauhan.preeti@gmail.com

# **Process Integration**

Chair Anisur Rahman Anisur.rahman@intel.com

Vice-Chair Guido Sasse Guido.sasse@nxp.com

# **Reliability Testing**

Chair Osama O. Awadelkarim OOAESM@engr.psu.edu

Vice Chair Yi Zhao yizhao@zju.edu.cn

# RF/mmW/5G Reliability

Chair Jose Jimenez jose.jimenez@Qorvo.com

Vice-Chair Fernando Guarin fernando.guarin@globalfoundries.com

#### **Soft Error**

Chair Daisuke Kobayashi d.kobayashi@isas.jaxa.jp Vice-Chair Yanran Chen yanranpa@xilinx.com

# System Electronics Reliability

Chair Flavio Griggio flavio.griggio@microsoft.com

Vice-Chair Yan Liu yan.liu@medtronic.com

#### **Transistors**

Chair Chetan Prasad chetan.prasad@intel.com

Vice Chair Bonnie Wier bonnie.weir@broadcom.com

### Wide-Bandgap Semiconductors-GaN

Chair Sameh Khalil Sameh.Khalil@infineon.com

Vice Chair Joshi Kaustabh joshi.kaustabh@intel.com

### Wide-Bandgap Semiconductors-SiC

Chair Thomas Aichinger

Thomas.Aichinger@infineon.com

Vice chair Daniel Lichtenwalner daniel.lichtenwalner@wolfspeed.com

# Topics of Interest SPECIAL FOCUS TOPICS

Circuit Reliability and Aging – RAS, self-healing, aging aware designs, design tools

Emerging memory / Neuromorphic Computing– Reliability for PCM, MRAM, RRAM, ferroelectrics

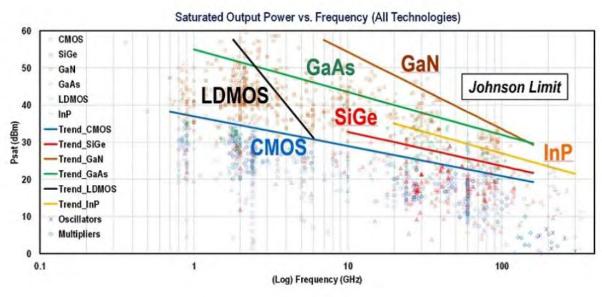

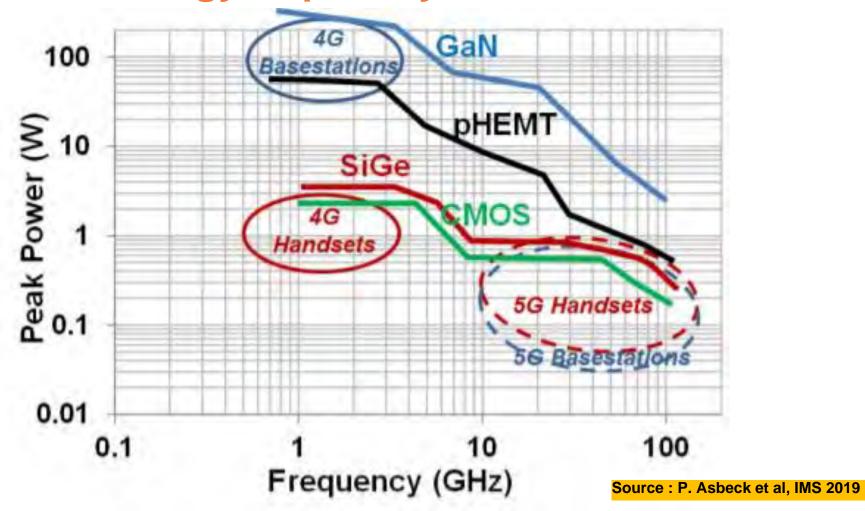

Reliability of RF/mmW/5G Devices – CMOS, SiGe BiCMOS, SOI, GaAs, GaN

# Circuits, Products, and Systems

**Circuit Reliability and Aging -** Includes digital, mixed-signal, power and RF applications; design for reliability; variability-aware design, EDA tools and compact modeling

**IC Product Reliability** – Includes burn-in; Early Failure Rate; defect detection; on-chip sensors; failure analysis; modeling; product reliability estimation; multichip product; stacked and HBM memory; DFT/DFR solutions for improved reliability; chiplet reliability considerations

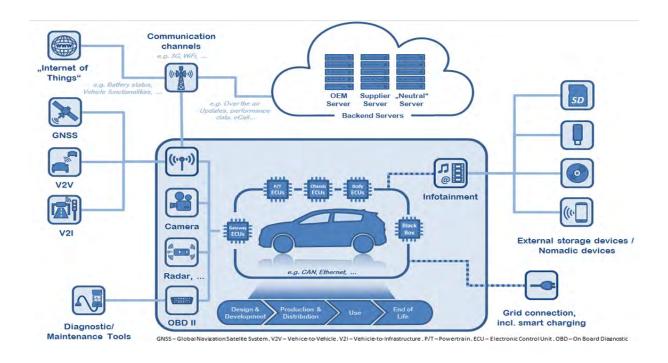

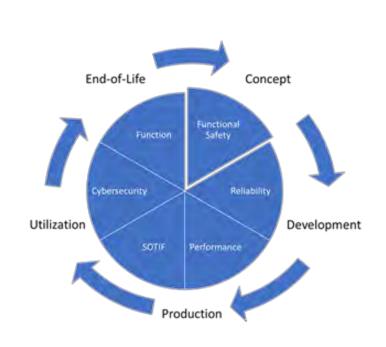

**System Electronics Reliability** – Includes reliability of electronic systems including personal computing, data center, storage, networking, communication, healthcare, automotive, portable devices, space, display and energy; architecture and design methods to manage system reliability including "row hammer" scenarios; system monitoring, modeling and health prognostics; system qualification for reliability including screening techniques and failure root cause determination; extreme temperatures from cryogenic to 150C.

**Soft Errors –** Includes impact of neutrons, alpha particles, protons and heavy ions on electronics, photonic devices and systems; Device, circuit, system and application level simulation and mitigation techniques for single-bit/multi-bit single event effects in memories and logic.

**ESD and Latchup** - Includes component and system-level ESD design; modeling and simulation

**Packaging and 2.5D/3D Assembly –** Includes chip-package interaction; fatigue; power dissipation issues; reliability of 2.5D and 3D IC packaging and TSV integration, interconnects, multichip modules, passive interposers

**Reliability Testing** – Includes reliability equipment, tools, test structures, and test methods; design for reliability testing **Silicon Photonics** – Including reliability of integrated silicon photonics systems RF/mmW/5G – Reliability of CMOS, BiCMOS, SiGe, SOI, III-V and other devices in high frequency applications

# Materials, Processing, and Devices

**Transistors** – Includes hot carrier phenomena; BTI; RTN; advanced node scaling; variability; Ge and III-V channels; nano-wire, gate all-around, nano-ribbon, fork-sheet devices

**Gate/MOL/BEOL Dielectrics** – Includes reliability of novel gate dielectrics and ferroelectrics; 2D layered dielectrics and van der Waals dielectrics for 2D materials based devices; modeling of dielectric breakdown; gate dielectric reliability for III-V, Ge, and advanced FETs; middle-of-the-line reliability; MIM/MOM capacitors; low-k dielectric breakdown

**Beyond CMOS Devices –** Includes reliability of tunnel FETs, transistors with 2D semiconductors (graphene, MoS2); ferroelectric and negative capacitance FETs; spintronics

**Neuromorphic Computing Reliability -** Reliability of devices logic and memory (MRAM, RRAM, etc) and design architectures used in neuromorphic computing Gallium-Nitride and Silicon-Carbide Wide-Bandgap

**Semiconductors** – Threshold voltage instabilities, charge trapping, switching stress, breakdown and other reliability topics including thermal issues within power devices.

Compound and Optoelectronic Devices – Includes reliability of III-V-based devices; optoelectronic devices; far infrared detectors

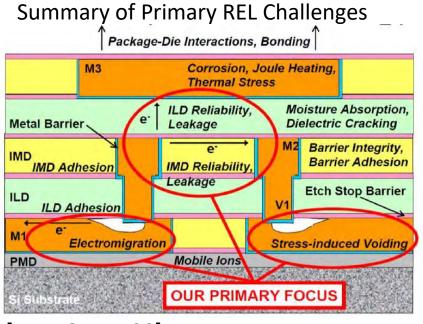

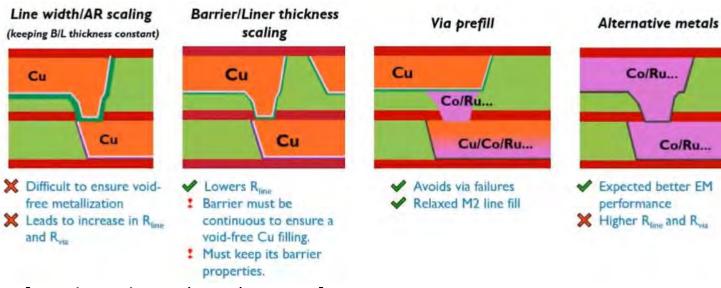

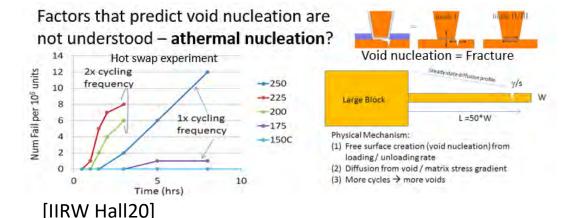

**Metallization/BEOL Reliability -** Includes electromigration; Joule heating; stress migration; Process Integration – Includes new process-related reliability issues; foundry reliability challenges

Failure Analysis - Includes evidence of new failure mechanisms; advances in failure analysis techniques

**Memory Reliability –** Includes stand-alone DRAM and 3DNAND; emerging memory devices such as STT MRAM, RRAM, ferroelectrics, and PCM.

MEMS - Includes reliability of sensors and actuators; reliability testing; analysis & modeling; BioMEMS

# **Program**

NOTE – For full Program, including Abstracts and Speaker information, view Appendix VIDEOS – https://www.youtube.com/user/IEEEIRPS/videos

# **Keynote Speakers**

#### Memory's journey towards the future information and communications technology (ICT) world

President & CEO of SK hynix

Seok-Hee Lee

Seok-Hee Lee is the president and chief executive officer of SK hynix. He has led the innovation of memory and CIS technology to secure the company's growth ever since he was appointed to the position in December 2018. Most recently, he drove the acquisition of Intel's NAND business, as announced in 2020.

Previously, he held several leadership positions at SK hynix. In 2013, he headed R&D, as the senior vice president and chief technology officer, overseeing the development of all the new semiconductor technologies and processes. From 2014, he headed DRAM Development Business, driving the development of DRAM process technology for further scaling. From 2016, prior to becoming the CEO, Dr. Lee served as the company's chief operating officer, responsible for all of the company's business.

Dr. Lee first joined Hyundai Electronics (now, SK hynix) in 1990, and worked as a senior researcher. From 2000, he worked at Intel, as a principal engineer and a group leader, responsible for process improvement. From 2010 to 2013, he was the Associate Professor of Electrical and Electronic Engineering at KAIST(Korea Advanced Institute of Science and Technology), where his research was primarily on scaling and manufacturing semiconductors.

Dr. Lee received Ph.D. in Materials Science and Engineering from Stanford University, and both M.S and B.S in Inorganic Materials Science and Engineering from Seoul National University.

#### SiC MOSFET Reliability: An overnight success 30 years in the making

John Palmour

CTO Cree /Wolfspeed

#### Laying the Groundwork for 6G communications

Peter Gammel

CTO MWI at GlobalFoundries

#### IoT End-node Device: Built to Last

Alessandro Piovaccari

CTO Silicon Labs

(in cooperation with IEW)

# **Invited Speakers**

#### Wide-Bandgap Semiconductors- GaN

2B.1 (Invited) - Progress and Current Topics of JEDEC JC-70.1 Power GaN Device Quality and Reliability Standards

Activity – Tim McDonald, Infineon, Chair, JEDEC JC-70.1 / Stephanie Watts Butler, Texas Instruments, Chair, JEDEC

JC-70

#### **Neuromorphic Computing Reliability**

- 2C.1 (Focus) Conductance variations and their impact on the precision of in-memory computing with resistive switching memory (RRAM) Daniele Ielmini, Politecnico di Milano

- 2C.2 (Focus) Embedded emerging memory technologies for neuromorphic computing: temperature instability and

- reliability Yao-feng Chang, Intel

- 2D.1 (Focus) Can Emerging Computing Paradigms Help Enhancing Reliability Towards the End of Technology Roadmap? Runsheng Wang, Peking University

#### RF/mmW/5G Reliability

- 3B.1 (Focus) New Developments in SiGe HBT Reliability for RF Through mmW Circuits John Cressler, Georgia Tech

- 3B.2 (Focus) Reliability and Failure Analysis of 100 nm AlGaN/GaN HEMTs under DC and RF Stress Michael Dammann, Fraunhofer Institute IAF

#### **Soft Error**

• 3D.1 (Invited) - Single Event Hard Error Due to Terrestrial Radiation - Jin-Woo Han, NASA Ames Research Center RF/mmW/5G Reliability

- 3E.1 (Focus) CMOS RF reliability for 5G mmWave applications Challenges and Opportunities Purushothaman Srinivasan, GlobalFoundries

- 3E.2 (Focus) Guidelines for Space Qualification of Gan HEMTs and MMICs John R. Scarpulla, The Aerospace Corporation

#### **Metallization/BEOL Reliability**

3F.1 (Invited) Back End Of Line Opportunities and Reliability Challenges for Future Technology Nodes – Mauro Kobrinsky, Intel Corporation

#### **Memory Reliability**

• 3H.1 (Invited) - Challenges of Flash Memory for Next Decade – Kazunari Ishimaru, Kioxia

#### **Circuit Reliability and Aging**

• 4A.1 (Invited) - Silicon Lifecycle Management with in-chip Monitoring - Rajesh Kashyap, Synopsys

#### Packaging and 2.5/3D Assembly

• 4D.1 (Invited) Reliability of Optoelectronic Module: An overview – John Osenbach, Infinera

#### **Emerging Memory Reliability**

- 5B.1 (Focus) Reliability of STT-MRAM for Various Embedded Applications Shinhee Han, Samsung Electronic

- 5B.2 (Focus) Challenges toward Low-Power SOT-MRAM Shy-Jay Lin, TSMC

#### Wide-Bandgap Semiconductors- SiC

- 5C.1 (Invited) Is There a Perfect SiC MOSFET Device on an Imperfect Crystal? Thomas Neyer, ON Semiconductor

- 5C.5 (Invited) Space Radiation Effects on SiC Power Device Reliability Jean-Marie Lauenstein, NASA Goddard Space Flight Center

#### **Emerging Memory Reliability**

- 5D.1 (Focus) Reliability aspects of ferroelectric hafnium oxide for application in non-volatile memories Thomas Mikolajick, NamLab and IHM, TU Dresden

- 5D.2 (Focus) Ultrathin Ferroelectricity and Its Application in Advanced Logic and Memory Devices Sayeef Salahuddin, UC Berkeley

# **Tutorials**

- Tut1 Reliability Challenges with 3D Integration of Semiconductor Packaging Enamul Kabir Intel

- Tut2 Practical Applications of Bayesian Reliability Yan Liu Medtronic

- Tut3 Methodologies for Device Reliability Testing: From DC to Sub-ns Yi Zhao Zhejiang University

- Tut4 5G/mmW/RF- Silicon / 5G/mmW/RF-GaN Fernando Guarin Globalfoundries / Don Gajewski Wolfspeed

- Tut5 Neuromorphic Computing Brian Hoskins NIST

- Tutó Calculation of Terrestrial Cosmic Ray Displacement Damage Melanie Raine CEA

- Tut7 Understanding and Challenges of MOL/BEOL TDDB Reliability Andrew Kim Intel

- Tut8 GaN Reliability Enrico Zanoni University of Padova

- Tut9 High-K Dielectrics on Non Silicon Semiconductors Chadwin Young University of Texas Dallas

- Tut 10 Advanced 3D Flash Memory Architectures Hang Ting Lue Macronix

- Tutl 1 Magnetic Resonance Techniques Mark Anders NIST

- Tut12 DRAM Reliability Overview Hokyung Park SK hynix

- Tut13 Hot-carrier Degradation in Si Devices from Experimental Observations to Accurate Physical Modeling -Stanislav Tyaginov - IMEC

- Tut 14 Metal reliability for advanced interconnects Olalla Varela IMEC

- Tut15 Automotive Andreas Aal Volkswagen (in cooperation with IEW) / Oliver Aubel Globafoundries

- Tut16 Reliability and Performance Limiting Defects in 4H SiC Metal Oxide Semiconductor Field Effect Transistors -Patrick Lenahan- Penn State University

- Tut17 Application and characterization of CMOS cryogenic electronics Pragya Shrestha NIST

- Tut18 Electronic Design Automation (EDA) Solutions for Latch-up Verification in CMOS and HV Technologies -Michael Khazhinsky - Silicon Labs (in cooperation with IEW)

- Tut19 EOS, ESD, Transient, AMR, EIPD, Robustness, Aging Do All of These Pieces go to the Same Puzzle? -Hans Kunz - Texas Instruments (in cooperation with IEW)

- Tut20 Exploring Relation of ESD and EMC: Tests, Events to Damage, Failure Types, and Co-Design Approaches Alan Righter Analog Devices

- Tut21 FinFET Self-heating: Measurements, Concerns and Applications Zakariae Chbili Intel (in cooperation with IEW)

- Tut22 Full chip CDM ESD Verification Melanie Etherton NXP

# Workshops

- WS1 Device Reliability Xavier Federspiel (ST) / Souvik Mahapatra (IIT)

- WS2 SSD Memory Jay Sarkar (Micron Technologies)

- WS3 BEOL Ki-don Lee (SEC) / Gavin Hall (OnSemi)

- WS4 Wide Band Gap (SiC) Dr. Ron Green (CIV USARMY CCDC ARL (USA)) / Thomas Aichinger (Infineon)

- WS5 Neuromorphic Gennadi Bersuker (Aerospace Corp.) / Pey Kin Leong (SUTD) / Matt Marinella (Sandia)

- WS6 HV transient IEC ESD Design Challenges (in cooperation with IEW) Raj Sankaralingam (TI) / Alan Righter (Analog Devices)

- WS7 Circuit Reliability and Aging: Measurements and Simulations Valeriy Sukharev (Mentor) / Georgios Konstadinidis (Google)

- WS8 Emerging Memory Joe McCrate (Micron) / Tetsuo Endoh (Tohoku University)

- WS9 Automotive for in-car safety and security Jyotika Athavale (Nvidia) / Udeerna Doppalapudi (Qualcomm)

- WS10 Wide Band Gap (GaN) Shireen Warnock (MIT LL) / Matteo Meneghini (UniPD))

- WS11 RF/mmW/5G Fernando Guarin (Globalfoundries) / Sriram Kalpat (Qualcomm)

# **Year In Review**

- YIR1 (Year-in-Review) FinFET vs GAA: Main reliability Differences and Concerns Presented by Adrian Chasin (imec)

- YIR2 (Year-in-Review) Reliability Testing: Considerations for Physics-Based Reliability Testing Development Presented by Derek W. Slottke (Intel)

- YIR3 (Year-in-Review) Industry Council on ESD Target Levels: Review of Achievements, Activities, and Initiatives -Presented by Charvaka Duvvury (ESD Consulting) – in cooperation with IEW

# **Highlighted Papers**

- 2B.5 Study on the Difference between ID(VG) and C(VG) pBTI Shifts in GaN-on-Si E-Mode MOSc-HEMT A.G. Viey, W. Vandendaele, M.-A. Jaud, J. Coignus, J. Cluzel, A. Krakovinsky, S. Martin, J. Biscarrat, R. Gwoziecki, V. Sousa, F. Gaillard, University Grenoble-Alpes, R. Modica, F. Iucolano, Research and Development Department STMicroelectronics, M. Meneghini, G. Meneghesso, University of Padova Via Gradenigo 6/B, G. Ghibaudo, IMEP-LAHC MINATEC University Grenoble-Alpes

- 5D.3 Elucidating 1S1R Operation to Reduce the Read Voltage Margin Variability by Stack and Programming Conditions Optimization - J. Minguet Lopez, L. Hudeley, L. Grenouillet, D. Alfaro Robayo, J. Sandrini, G. Navarro, M. Bernard, C. Carabasse, D. Deleruyelle, N. Castellani, M. Bocquet, J. M. Portal, E. Nowak, G. Molas, 1CEA, Aix Marseille Univ, INL CNRS

- 2A.2 Characterization of Slow Traps in SiGe MOS Interfaces by TiN/Y2O3 Gate Stacks T.-E. Lee, K. Toprasertpong, M. Takenaka, S. Takagi, The University of Tokyo

- 3A.3 TDDB Reliability in Gate-All-Around Nanosheet Huimei Zhou, Miaomiao Wang, Ruqiang Bao, Tian Shen, Ernest Wu, Richard Southwick, Jingyun Zhang, Veeraraghavan Basker, Dechao Guo, IBM Research Division

- 5A.3 Time Dependent Variability in Advanced FinFET Technology for End-of-Lifetime Reliability Prediction Hai Jiang, Jinju Kim, Kihyun Choi, Hyewon Shim, Hyunchul Sagong, Junekyun Park, Hwasung Rhee, Euncheol Lee, Technology Quality and Reliability Group

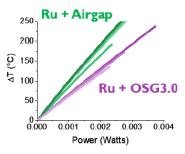

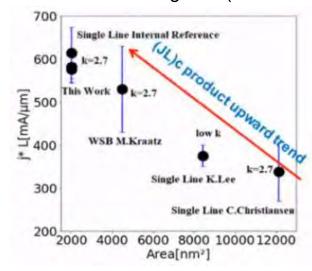

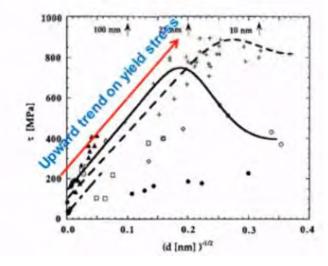

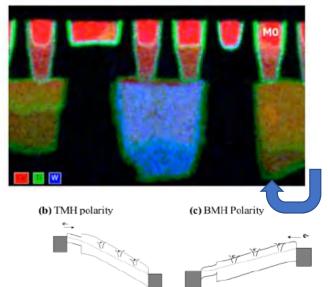

- 3F.2 Reliability of a DME Ru Semidamascene Scheme with 16 nm wide Airgaps A. Lesniewska, O. Varela Pedreira,

M. Lofrano, G. Murdoch, M. van der Veen, A. Dangol, N. Horiguchi, Zs. Tokei, K. Croes, imec

- 2C.3 Characterization and Mitigation of Relaxation Effects on Multi-level RRAM Based in-Memory Computing -Wangxin He, Wonbo Shim, Shihui Yin, Xiaoyu Sun, Deliang Fan, Shimeng Yu, Jae-sun Seo, Arizona State University, Georgia Institute of Technology

- 4D.3 Reliability of Wafer-Level Ultra-Thinning Down to 3 µm using 20 nm-Node DRAMs Zhwen Chen, Youngsuk Kim, Tadashi Fukuda, Koji Sakui, Takayuki Ohba, Tokyo Institute of Technology, DISCO Corporation, Omori-Kita 2-chome, Tatsuji Kobayashi, Takashi Obara, Micron Memory Japan

- 4A.2 Reliability and Variability-Aware DTCO Flow: Demonstration of Projections to N3 FinFET and Nanosheet Technologies G. Rzepa\*, M. Karner\*, O. Baumgartner\*, G. Strof\*, F. Schanovsky\*, F. Mitterbauer\*, C. Kernstock\*, H.W. Karner\*, P. Weckx•, G. Hellings•, D. Claes•, Z. Wu•◊, Y. Xiang•◊, T. Chiarella•◊, B. Parvais•°, J. Mitard•, J. Franco•, B. Kaczer•, D. Linten•, Z. Stanojevic\*, \*Global TCAD Solutions, •imec, ◊ KU Leuven, ° Vrije Universiteit Brussels

- 3G.3 Compact Model of ESD Diode Suitable for Sub-Nanosecond Switching Transients Shudong Huang, Elyse Rosenbaum, University of Illinois at Urbana-Champaign

- 2D.2 Robust Brain-Inspired Computing: On the Reliability of Spiking Neural Network using Emerging Non-Volatile Synapses - Ming-Liang Wei 1,2, Hussam Amrouch 3, Cheng-Lin Sung 1, Hang-Ting Lue 1, Chia-Lin Yang 2, Keh-Chung Wang 1, Chih-Yuan Lu 1, 1-Macronix International Co., Ltd., 2-National Taiwan University, 3-University of Stuttgart

- 3D.2 Scaling Trends in the Soft Error Rate of SRAMs from Planar to 5-nm FinFET B. Narasimham, V. Chaudhary, M. Smith, L. Tsau, Broadcom Inc, D. Ball, B. Bhuva, Vanderbilt University

- 4E.4 Machine Learning on Transistor Aging Data: Test Time Reduction and Modeling for Novel Devices Neel Chatterjee\*‡, John Ortega\*, Inanc Meric\*, Peng Xiao\*, Ilan Tsameret\*, \*Intel Corp., †University of Minnesota

- 3B.3 RF Reliability of SOI-Based Power Amplifier FETs for mmWave 5G Applications P. Srinivasan, F.Guarin, S. Syed, J. A. S. Jerome, W. Liu, S. Jain, D. Lederer, S. Moss, P. Colestock, A. Bandyopadhyay, N.Cahoon, B. Min, M. Gall, Globalfoundries Inc.

# **Poster Session**

See Appendix - Full Program for Poster Sessions

### **Exhibits & Exhibit Events**

Exhibits are an integral part of the International Reliability Physics Symposium. Don't miss this opportunity to showcase your company's products and services in our VIRTUAL exposition.

For more than 59 years, the International Reliability Physics Symposium (IRPS) has been the premier conference for engineers and scientists to present new and original work in the area of microelectronics reliability. Drawing participants from the United States, Europe, Asia, and other parts of the world, IRPS seeks to understand the interplay between the reliability of semiconductor components, integrated circuits, and microelectronic assemblies through an improved understanding of both the physics of failure as well as the application environment.

#### IRPS Highlights:

- 400+ professionals from the semiconductor reliability field

- 90+ platform presentations and invited talks

- 50+ posters at the evening reception

- 20+ tutorials

- 10+ workshops and panel discussions

For more information or for custom opportunities, contact Lisa Boyd – l.boyd@ieee.org

# IRPS gratefully acknowledges the generous support of our 2021 exhibitors:

Tektronix<sup>®</sup>

# **2021 IEEE International Reliability Physics Symposium (IRPS)**

Virtual Conference 21 March – 24 March 2021

# 2021 IEEE International Reliability Physics Symposium (IRPS 2021)

### Sunday, March 21

#### **Welcome & IRPS Introduction**

Sunday, March 21, 8:00 a.m. – 8:35 a.m. PDT Robert Kaplar, Sandia National Labs Chris Connor, Intel Charlie Slayman, Cisco Systems Venue: Monterey Main Stage

#### **Keynote 1**

Sunday, March 21, 08:35 a.m. – 09:20 a.m. PDT Robert Kaplar, Sandia National Labs Chris Connor, Intel Venue: Monterey Main Stage

08:35 a.m.

KN1 (Keynote) - Memory's Journey Towards the Future Information and Communications Technology (ICT) World, Seok-Hee Lee, CEO SK hynix

With the acceleration of digital transformation under the fourth industrial revolution, the COVID-19 pandemic has completely changed our daily lives, giving rise to digital healthcare, remote learning/conferencing, to name a few. Such transformation, along with the integration of AI and 5G network, is likely to help create new values from a vast pool of data, and is likely to lead us towards an era of information, communication, and technology, where large amounts of information are delivered with unprecedented speed and accuracy. To enable such transformation, increasingly high speed, low power, high capacity, and high reliability memory semiconductors are required. Within the memory semiconductor industry, we have continued to overcome the technological challenges of DRAM scaling and NAND flash stacking by making continuous improvements. However, the pace of semiconductor technology development is yet to catch up with the rate at which data is produced, which necessitates still more innovative semiconductor technologies to handle the explosive growth in data. In this speech, I would like to introduce SK Hynix's journey towards future technological advancement. Also, I would like to suggest finding solutions to problems together through the collaboration among the industry/academia/research, with a goal of making a better world with information and communications technologies (ICT) through sharing rather than through competition.

#### 2A – GD (Gate/MOL Dielectrics)

Sunday, March 21, 09:20 a.m. – 11:30 a.m. PDT Francesco Maria Puglisi, Università di Modena e Reggio Emilia Andrea Padovani, Applied Materials

Venue: Big Sur

#### 2A – Intro

09:20 a.m. - 09:25 a.m. PDT

09:25 a.m.

2A.1 (ESREF) - Assessing the Pre-Breakdown Carriers' Multiplication in SiC Power MOSFETs by Soft Gamma Radiation and its Correlation to the Terrestrial Cosmic Rays Failure Rate Data as Measured by Neutron Irradiation, Mauro Ciappa, Marco Pocaterra, ETH Zurich

The susceptibility to terrestrial cosmic rays (TCR) of power devices is strongly correlated to the peak of the local electric field, thus to the resulting local carriers' multiplication. In this paper, the soft gamma radiation from an Am<sup>241</sup> source is used to characterize the pre-breakdown carriers' multiplication in SiC MOSFETs as a function of the applied blocking bias. The resulting multiplication levels are then compared to TCR failure rate literature data assessed by neutron irradiation.

09:50 a.m.

**2A.2 - Characterization of Slow Traps in SiGe MOS Interfaces by TiN/Y<sub>2</sub>O<sub>3</sub> Gate Stacks, T.-E. Lee\***, K. Toprasertpong, M. Takenaka, S. Takagi, The University of Tokyo

We have examined the slow electron and hole trap density at  $TiN/Y_2O_3/SiGe$  MOS interfaces. The effect of trimethylaluminum (TMA) pre-treatment before  $Y_2O_3$  deposition on the slow trap density has been studied. Also, the dependency of the slow trap density on Ge contents of SiGe has been systematically evaluated and the influence of the composition of interfacial layers (ILs) is examined. It is found that 10-cycle TMA treatment is effective to suppress the formation of slow traps attributable to Ge-O bonds in ILs. On the other hand, the density of electron and hole slow traps in the  $Y_2O_3/SiGe$  MOS interfaces increases with higher Ge content of SiGe, which can be explained by the formation of vacancy-related defects due to incorporation of Ge-O bonds into SiO<sub>2</sub> IL networks.

10:15 a.m.

**2A.3 - Off-State TDDB in FinFET Technology and its Implication for Safe Operating Area,** M. Toledano-Luque, P. Paliwoda, M. Nour, T. Kauerauf, B. Min, G. Bossu, M. Siddabathula, Fab 1 Reliability, T. Nigam, GlobalFoundries

Standard CMOS reliability has been focused on digital applications and the user profiles associated with these products. However, emerging applications in mobility, automotive, communication networks and data centers require additional, more rigorous reliability specifications. For these applications, the devices operate beyond the typical safe operation area (SOA) mostly because large drain biases are applied during the normal operation. In this situation, off-state TDDB could be a concern and it must be considered during product design. In this study, we present the models to describe off-state TDDB and the methodology to accurately predict the SOA for circuits under standard operation condition in field. The presented SOA approach relaxed the stringent reliability requirements defined on DC operation, reducing design overhead, and developing and verification costs.

10:40 a.m.

**2A.4** - Drastic Reliability Improvement using  $H_2O_2/UV$  Treatment of  $HfO_2$  for Heterogeneous Integration, S.M.  $Kim^{12}$ , T.M.H. Nyugen<sup>3</sup>, J.W. Oh<sup>3</sup>, Y.S. Lee<sup>12</sup>, S C.  $Kang^4$ , H.I. Lee<sup>12</sup>, C.H.  $Kim^{12}$ , S. Some<sup>12</sup>, H.J. Hwang<sup>12</sup>, B.H. Lee<sup>12\*</sup>, <sup>1</sup>Center for Semiconductor Technology Convergence, <sup>2</sup>Pohang

University of Science and Technology (POSTECH), <sup>3</sup>Gwangju Institute of Science and Technology (GIST), <sup>4</sup>Electronics and Telecommunications Research Institute (ETRI)

For heterogeneous integration, the heat cycle constraint limits the available number of options for the process of fabricating high-quality reliable high-k dielectrics, for example, post-deposition annealing and high-temperature deposition. To solve this problem, we examine the effects of  $H_2O_2/UV$  treatment on the reliability characteristics of low-temperature-grown  $HfO_2$  via atomic layer deposition, wherein it is treated with a minimal post-deposition heat cycle. The leakage current and time zero dielectric breakdown characteristics of the  $H_2O_2/UV$ -treated  $HfO_2$  are drastically improved without having applied the post-deposition heat cycle, compared with those of the control group that undergoes  $O_2$  post-deposition annealing. The proposed process is a promising method to improve the quality of dielectrics for heterogeneous integration.

11:05 a.m.

**2A.5 - Modeling of HKMG Stack Process Impact on Gate Leakage, SILC and PBTI,** Dimple Kochar, Tarun Samadder, Subhadeep Mukhopadhyay, Souvik Mahapatra, Department of Electrical Engineering Indian Institute of Technology Bombay (IIT Bombay)

Gate stack process (pre-clean, IL, IL/HK interface, HK, post-HK Nitridation) impact on gate leakage, SILC and PBTI is analyzed. IL and HK thickness, channel/IL and IL/HK energy-barrier offsets impact on gate leakage and SILC response from generated bulk traps inside IL and HK is quantified. Time kinetics of generated IL and HK bulk traps for SILC, and IL/HK interface traps for PBTI are simulated by a generic Reaction-Diffusion-Drift (RDD) framework. Model is validated using measurements from differently processed HKMG stacks.

#### 2A - Authors' Corner

11:30 a.m. – 12:00 p.m. PDT

#### 2B - GaN (Wide-Bandgap Semiconductors - GaN)

Sunday, March 21, 09:20 a.m. – 11:30 a.m. PDT Kaustubh Joshi, Intel Corporation Luca Perniola, CEA/LETI Venue: Carmel

2B – Intro

09:20 a.m. – 9:25 a.m. PDT

09:25 a.m.

**2B.1** (Invited) - Progress and Current Topics of JEDEC JC-70.1 Power GaN Device Quality and Reliability Standards Activity Or: What is the Avalanche Capability of Your GaN Transistor?, Infineon, Chair, JEDEC JC-70.1, Stephanie Watts Butler, Texas Instruments, Chair, JEDEC JC-70

"What is the avalanche (UIS or undamped inductive switching) capability of a GaN based power transistor?" is a question that is commonly posed in supplier / customer interactions today. The history, motivation and use of this rating (as applied to silicon based power MOSFETs) will be reviewed and its suitability for use with GaN based power HEMTs considered. UIS testing methods and standards are shown not to be a relevant gage of application robustness for GaN based power devices. Thus, for GaN devices, a gap exists between designer needs and existing industry standards. The state of supplier ratings to meet the gap is briefly highlighted and demonstrates why JEDEC subcommittee JC-70.1 should create relevant new standards for GaN overvoltage/ surge robustness. Finally, a brief review of overall JEDEC JC-70.1 scope, structure, process, and progress is provided.

09:50 a.m.

**2B.2 - Failure Mechanisms of Cascode GaN HEMTs under Overvoltage and Surge Energy,** Qihao Song\*, Ruizhe Zhang, Joseph P. Kozak, Jingcun Liu, Qiang Li Yuhao Zhang\*, Virginia Polytechnic Institute and State University

This work, for the first time, studies the surge-energy robustness and failure mechanisms of 650-V rated cascode GaN HEMTs in the unclamped inductive switching (UIS) tests. Different from the p-GaN HEMT which has a purely electric failure, two failure modes were observed, both occurring in the GaN HEMT. The cascode HEMT failure can be either electrically induced or thermally related. A preliminary explanation was proposed for the failure mechanisms under different load inductance.

10:15 a.m.

**2B.3 - Vertical Stack Reliability of GaN-on-Si Buffers for Low-Voltage Applications,** E. Fabris, M. Borga, N. Posthuma, M. Zhao, B. De Jaeger, S. You, S. Decoutere, imec, M. Meneghini, G. Meneghesso, E. Zanoni, University of Padova

In this paper the reliability of the vertical GaN-on-Si stack for lateral p-GaN HEMTs dedicated to low-voltage applications is discussed in detail by comparing wafers with different buffer thicknesses and growth condition of the AlN nucleation layer. The vertical robustness and the time-dependent vertical breakdown will be investigated in detail, demonstrating that the buffers with reduced thickness are suitable for 100 V applications. Moreover, the voltage drop on the different layers of the vertical stack will be extracted at the breakdown, and a model able to explain the degradation of the vertical stack will be proposed.

10:40 a.m.

**2B.4 - A** Generalized Approach to Determine the Switching Reliability of GaN HEMTs on-Wafer Level, Nicola Modolo<sup>1</sup>, Andrea Minetto<sup>2</sup>, Carlo De Santi<sup>1</sup>, Luca Sayadi<sup>1</sup>, Sebastien Sicre<sup>2</sup>, Gerhard Prechtl<sup>2</sup>, Gaudenzio Meneghesso<sup>1</sup>, Enrico Zanoni<sup>1</sup>, Matteo Meneghini<sup>1</sup>, 1. University of Padova, 2. Infineon Technologies Austria

A detailed analysis of the turn-on behavior of E-mode p-GaN HEMT is reported. A novel system has been developed to investigate the impact of hard-switching stress in terms of dynamic on-resistance, turn-on switching locus, and power dissipation. The novelty of our approach comes from the high speed of the turn-on commutations (in the range of 10 V/ns), enabling a realistic assessment of the power device performances before the packaging-level, thus shortening the technological development loop.

11:05 a.m.

**2B.5** - Study on the Difference between ID(VG) and C(VG) pBTI Shifts in GaN-on-Si E-Mode MOSc-HEMT, A.G. Viey, W. Vandendaele, M.-A. Jaud, J. Coignus, J. Cluzel, A. Krakovinsky, S. Martin, J. Biscarrat, R. Gwoziecki, V. Sousa, F. Gaillard, University Grenoble-Alpes, R. Modica, F. Iucolano, Research and Development Department STMicroelectronics, M. Meneghini, G. Meneghesso, University of Padova Via Gradenigo 6/B, G. Ghibaudo, IMEP-LAHC MINATEC University Grenoble-Alpes

In this paper, we investigate the difference between I D (V G ) and C(V G ) pBTI shifts on GaN-on-Si E-mode MOS-channel HEMTs, under various gate voltage stresses V GStress and temperatures T. A new experimental setup using ultra-fast simultaneous I D (V G ) and C(V G ) enables to monitor V TH drift through two metrics,  $\Delta V$  THI and  $\Delta V$  THC . TCAD simulations supports that I D (V G ) shift ( $\Delta V$  THI ) is related to charge trapping at the gate corners regions, while C(V G ) shift ( $\Delta V$  THC ) is ascribed to the gate bottom.

**2B – Authors' Corner** 11:30 a.m. – 12:00 p.m. PDT

#### **2C – NC** (Neuromorphic Computing Reliability)

Sunday, March 21, 09:20 a.m. – 11:30 a.m. PDT Stefano Ambrogio, IBM Research – Almaden

Venue: Pebble Beach

2C - Intro

09:20 a.m. – 09:25 p.m. PDT

09:25 a.m.

**2C.1** (Focus) - Conductance Variations and their Impact on the Precision of in-Memory Computing with Resistive Switching Memory (RRAM), Giacomo Pedretti<sup>1</sup>, Elia Ambrosi<sup>1</sup>, Daniele Ielmini<sup>1\*</sup>, <sup>1</sup>Politecnico di Milano and IU.NET

This work addresses the reliability of RRAM, with a focus on conductance variation and its impact on in-memory computing (IMC). The core advantage of IMC is the ability to execute matrix-vector multiplication (MVM) in one step in crosspoint memory arrays, which can significantly accelerate data-intensive computing tasks, such as the inference and training of deep neural networks (DNNs). Since MVM is executed in the analogue domain, the imprecision of weight parameters stored in the memory array can result in errors which can affect the accuracy of the computation. By referring to a typical IMC device, that is the resistive switching memory (RRAM), we describe the conductance variations and stability with time, high-lighting their impact on IMC accuracy. Then we discuss various options for mapping coefficients in the memory device, including multilevel, binary, unary, redundancy and slicing schemes, and their robustness with respect to conductance errors. It turns out that a tradeoff exists between accuracy and memory area occupation in the IMC circuit. Accurate IMC circuits thus must rely on the co-design of highly-precise, highly-stable devices and error tolerant mapping/computing schemes.

09:50 a.m.

**2C.2** (Focus) - Embedded Emerging Memory Technologies for Neuromorphic Computing: Temperature Instability and Reliability, Yao-Feng Chang<sup>1</sup>, Ilya Karpov<sup>1</sup>, Reed Hopkins<sup>2</sup>, David Janosky<sup>2</sup>, Jacob Medeiros<sup>2</sup>, Benjamin Sherrill<sup>2</sup>, Jiahan Zhang<sup>2</sup>, Yifu Huang<sup>2</sup>, Tanmoy Pramanik<sup>1</sup>, Albert Chen<sup>1</sup>, Tony Acosta<sup>1</sup>, Abdullah Guler<sup>1</sup>, James A. O'Donnell<sup>1</sup>, Pedro A Quintero<sup>1</sup>, Nathan Strutt<sup>1</sup>, Oleg Golonzka<sup>1</sup>, Chris Connor<sup>1</sup>, Jack C Lee<sup>2</sup>, Jeffrey Hicks<sup>1</sup>, 1. Intel Corporation, 2. The University of Texas at Austin

The impact of temperature instability of resistive memory switching on potential neuromorphic computing applications has been extensively studied using eNVM-R and eNVM-M technologies developed on Intel 22FFL process. The reliability risk assessment shows that the effects of ambient temperature (e.g. resistance or conductance shifting with varying temperature) can lead to potential degradation of the neural network accuracy. Our results provide additional insight into device-level physical models and circuit-level design guidance for potential AI hardware applications.

10:15 a.m.

**2C.3 - Characterization and Mitigation of Relaxation Effects on Multi-level RRAM Based in-Memory Computing,** Wangxin He<sup>1</sup>, Wonbo Shim<sup>2</sup>, Shihui Yin<sup>1</sup>, Xiaoyu Sun<sup>2</sup>, Deliang Fan<sup>1</sup>, Shimeng Yu<sup>2</sup>, Jae-sun Seo<sup>1, 1</sup>Arizona State University, <sup>2</sup>Georgia Institute of Technology

In this paper, we investigate the relaxation effects on multi-level resistive random access memory (RRAM) based in-memory computing (IMC) for deep neural network (DNN) inference. We characterized 2-bit-per-cell RRAM IMC prototypes and measured the relaxation effects over 100 hours on multiple 8 kb test chips, where the relaxation is found to be most severe in the two intermediate states. We incorporated the experimental data into SPICE simulation and software DNN inference, showing DNN accuracy for CIFAR-10 dataset could degrade from 87.35% to 11.58% after 144 hours. To recover the largely degraded accuracy, mitigation schemes are proposed: 1) at the circuit level, the reference voltage for RRAM IMC could be calibrated after 80 hours when the relaxation is saturated. 2) At the algorithm level, the weights are trained

with lower percentages to be quantized to the two intermediate states. With both schemes applied, the accuracy could be recovered to 87.32% for long-term stability.

10:40 a.m.

**2C.4 - Optimized Programming Algorithms for Multilevel RRAM in Hardware Neural Networks,** Valerio Milo<sup>1</sup> \*, Francesco Anzalone<sup>1</sup>, Cristian Zambelli<sup>2</sup>, Eduardo Pérez<sup>3</sup>, Mamathamba K. Mahadevaiah<sup>3</sup>, Óscar G. Ossorio<sup>4</sup>, Piero Olivo<sup>2</sup>, Christian Wenger<sup>3/5</sup>, Daniele Ielmini<sup>1</sup>, <sup>1</sup>Politecnico di Milano and IU.NET, <sup>2</sup>Università degli Studi di Ferrara, <sup>3</sup>IHP-Leibniz-Institut für innovative Mikroelektronik, <sup>4</sup>Universidad de Valladolid, <sup>5</sup>BTU Cottbus-Senftenberg

A key requirement for RRAM in neural network accelerators with a large number of synaptic parameters is the multilevel programming. This is hindered by resistance imprecision due to cycle-to-cycle and device-to-device variations. Here, we compare two multilevel programming algorithms to minimize resistance variations in a 4-kbit array of HfO<sub>2</sub> RRAM. We show that gate-based algorithms have the highest reliability. The optimized scheme is used to implement a neural network with 9-level weights, achieving 91.5% (vs. software 93.27%) in MNIST recognition.

11:05 a.m.

**2C.5 - Transient Investigation of Metal-Oxide Based, CMOS-Compatible ECRAM,** Paul M. Solomon\*, Douglas M. Bishop, Teodor K. Todorov, Simon Dawes, Damon B. Farmer, Matthew Copel, Ko-Tao Lee, John Collins, John Rozen, IBM Thomas J. Watson Research Center

Metal-oxide based Electrochemical Random-Access Memory (MO-ECRAM) has shown unique potential as a nonvolatile element for analog in-memory computation of deep learning tasks. Using a specially designed interdigitated device geometry, we investigate transient effects of MO-ECRAM and correlate them with programming speed, read speed and read-after write speed. Programming speed is shown to exponentially increase with programming voltage. Read speed reached the ns range, while read-after-write delay can be limited by decay of write transients in the studied devices. Two mechanisms of channel modulation were found; a prompt field effect and a field-induced memory effect. The charge control of the prompt effect was vastly greater than that of the memory effect. So to reduce and mitigate transient impact, we discuss both device improvements, and learning algorithm engineering strategies.

**2C – Authors' Corner** 11:30 a.m. – 12:00 p.m. PDT

#### **Tutorial 1**

Sunday, March 21, 09:20 a.m. – 10:50 a.m. PDT Prem Chirayarikathuveedu, Consultant Preeti Chauhan, Google Venue: Monterey Main Stage

09:20 a.m.

**TuT1** (**Tutorial**) - **Reliability Challenges with 3D Integration of Semiconductor Packaging**, Mohammad Kabir, Intel Corporation

Process technology scaling has driven the need for advancement in semiconductor packaging technology to address insatiable demand in performance, power and form factor. A growing number of innovative 3D package assembly technologies have evolved to enable semiconductor industry to maximize products functionality. This tutorial will cover history on packaging development with focus on 3D integrations. In-depth reliability studies of 3D integration of packaging technologies will be discussed along with some general industry perspective on future roadmaps.

#### **Exhibitor Meet & Greet**

11:20 a.m. – 03:00 p.m. PDT

#### Break

12:00 p.m. – 03:00 p.m. PDT

#### **2D – NC** (Neuromorphic Computing Reliability)

Sunday, March 21, 03:00 p.m. – 04:45 p.m. PDT John Paul Strachan, Hewlett Packard Labs Venue: Big Sur

#### 2D – Intro

03:00 p.m. – 03:05 p.m. PDT

03:05 p.m.

**2D.1** (Focus) - Can Emerging Computing Paradigms Help Enhancing Reliability Towards the End of Technology Roadmap?, Runsheng Wang<sup>1\*</sup>, Zuodong Zhang<sup>1</sup>, Yawen Zhang<sup>1</sup>, Yixuan Hu<sup>1</sup>, Yanan Sun<sup>2</sup>, Weikang Qian<sup>3</sup>, Ru Huang<sup>1</sup>, <sup>1</sup>Institute of Microelectronics, <sup>2</sup>Shanghai Jiao Tong University, <sup>3</sup>UM-SJTU Joint Institute and MoE Key Lab of Artificial Intelligence, Shanghai Jiao Tong University

With CMOS technology shrinking into nanoscale, the design margin has become extremely tight due to the severer transistor aging and process variations. We present a new perspective to enhance design reliability: using emerging computing paradigms. As the preliminary attempts, three reliability-enhanced design flows based on approximate computing and/or stochastic computing are demonstrated. The results show that some computing paradigms are inherently robust, or can trade off computing accuracy for reliability, providing designers with more flexibility.

03:30 p.m.

**2D.2 - Robust Brain-Inspired Computing: On the Reliability of Spiking Neural Network using Emerging Non-Volatile Synapses,** Ming-Liang Wei<sup>1,2</sup>, Hussam Amrouch<sup>3</sup>, Cheng-Lin Sung<sup>1</sup>, Hang-Ting Lue<sup>1</sup>, Chia-Lin Yang<sup>2</sup>, Keh-Chung Wang<sup>1</sup>, Chih-Yuan Lu<sup>1</sup>, <sup>1</sup>Macronix International Co., Ltd., <sup>2</sup>National Taiwan University, <sup>3</sup>University of Stuttgart

Reliability issues arise due to the characteristics of Non-Volatile Memory synapses operating under the limited circuit cost. Through a simulation study, we identified several criteria of the memory synapses for the membrane capacitor size of 1pF. (1) The required ON-OFF ratio needs to be >1000 to preserve classification accuracy. (2) Low ON-current Ion (<10uA) is preferred for low power. (3) The variation and error of Ion should be lower than +/- 10% of mean value.

03:55 p.m.

**2D.3 - Novel Weight Mapping Method for Reliable NVM Based Neural Network,** L.X.Han, Y.C.Xiang, P. Huang\*, G. H. Yu, R. Z. Han, X. Y. Liu, J. F. Kang, Institute of Microelectronics, Peking University

Errors of vector-matrix-multiplication induced by interconnect resistance become a crucial reliability challenge in non-volatile memory (NVM) based neural network. Here, we propose a novel weight mapping method, called weight mapping correction (WMC), to mitigate the deviation of weight represented by the conductance of NVM array without time-consuming retraining and circuit overheads. Simulation results show that accuracy is recovered significantly when WMC is applied to various size arrays consisting of mainstream NVM in advanced technology nodes.

04:20 p.m.

2D.4 - Low-Bit Precision Neural Network Architecture with High Immunity to Variability and Random Telegraph Noise Based on Resistive Memories, Tommaso Zanotti, Francesco Maria Puglisi, Paolo Pavan, Università di Modena e Reggio Emilia

In this work, we devise and train a low-bit precision neural network with binary weights and 4-bits activations and study the impact of RRAM nonidealities on the classification accuracy by means of full circuit-level simulations enabled by a physics-based RRAM compact model, calibrated on experimental data from the literature. Results show that combining binary weights with low-precision activations allows retaining software-level accuracy even in the presence of Random Telegraph Noise and weight variability.

#### 2D - Authors' Corner

04:45 p.m. – 05:10 p.m. PDT

#### **Tutorial 2**

Sunday, March 21, 03:00 p.m. – 04:30 p.m. PDT Chetan Prasad, Intel Corporation

03:00 p.m.

TuT2 (Tutorial) - Practical Applications of Bayesian Reliability, Yan Liu, Medtronic

This tutorial provides fundamental knowledge of Bayesian reliability and utilizes numerous examples to show how Bayesian models can solve real life reliability problems. It covers what Bayesian analysis is, what its benefits are, and how it can be applied to reliability engineering.

Basic concepts of Bayesian statistics, models, reasons, and computation are presented. The tutorial then goes on to cover Bayesian models for estimating system reliability and design capability; a discussion of Bayesian Hierarchical Models and their applications; and more. To help readers get started quickly, the tutorial presents Bayesian model examples that use JAGS and which require fewer than 10 lines of command, and short R scripts.

#### **Tutorial 3**

Sunday, March 21, 03:00 p.m. – 04:30 p.m. PDT Jim Ashton, NIST

03:00 p.m.

TuT3 (Tutorial) - Reliability Testing of Devices: From DC to Sub- ns Region, Yi Zhao, Zhejiang University

Conventionally, for both industry applications and research purposes, DC measurement methodology is adopted in semiconductor device characterizations. However, the clock frequency in real circuits has already been over GHz for many years and the devices, specially transistors, in the circuit also work in the sub-nano second (sub-ns) region, resulting in the strong demand for ultra fast device testing methodologies. On the other hand, traditional semiconductor parameters analyzing tools and methodologies still cannot capture the transient electrical properties of devices in the sub-ns time scale.

In this tutorial, we will first review the basics of DC device testing and then introduce ultra-fast device testing methodologies and measurement systems for both logic and memory devices. For logic devices, the impact of measurement speed on device parameter extractions will be discussed first upon considering the self heating effect and trap behaviors. And then the applications of nano second and sub-ns device testing methodologies to device reliability study will be introduced, including bias temperature instability, hot carrier degradation, and the self-heating effect in advanced technology nodes. As for new memories, device behavior

characterizations using ultra-fast device testing methodologies will be demonstrated for ferroelectric devices and MRAM.

#### **Tutorial 4**

Sunday, March 21, 03:00 p.m. – 04:30 p.m. PDT Jason Ryan, NIST

03:00 p.m.

TuT4 (Tutorial) - 5G/mmW/RF - Silicon & 5G/mmW/RF - GaN

Silicon Reliability for 5G/mmWave/RF Applications, Fernando Guarin, Purushothaman Srinivasan, GlobalFoundries

The reliability infrastructure developed for Silicon based logic applications is not sufficient to address the requirements for 5G circuits. This tutorial will provide a practical overview of the key reliability mechanisms along with the challenges faced by reliability engineers studying the reliability of 5G/mmWave/RF applications implemented with Silicon based technologies. We will review reliability within the context of scaling, power and integration showing how these have positioned the Silicon and Silicon Germanium technologies as viable contenders for very high speed, high integration and high reliability applications. We will show a practical approach to the reliability evaluation of Power Amplifiers operating in the 28 to 39 GHz range along with a discussion of the qualification methodologies required for the release of these technologies to the field. We will cover aspects of the development of reliability models that work under industry standard circuit simulators that provide circuit designers with the necessary tools to extract the maximum performance while achieving optimum reliability. A brief overview of Self heating and its characterization in Silicon based systems will be also be presented. Throughout this tutorial we will show several examples of reliability stress data along with the models to support our methodology and conclusions.

#### GaN RF Device Reliability for 5G/mmW Applications, Don Gajewski, Wolfspeed

In this tutorial, I will review the reliability failure mechanisms and predictive lifetime extrapolations published in the open literature for GaN RF devices for 5G/mmW applications. I will cover failure mechanisms including field plate electromigration, piezo-electric GaN cracking/pitting, ohmic contact degradation, trap generation, hot electron injection, Schottky gate contact degradation, through-SiC via degradation, field plate dielectric dielectric breakdown, hydrogen poisoning, and gate electromigration. I will give an overview of the DCand RF-driven accelerated life testing methods, data, and intrinsic lifetime predictions. I will also cover product level reliability aspects related to humidity, high junction temperatures and temperature cycling. Finally, I will discuss some of the key implications of these reliability aspects for 5G/mmW applications.

#### Reliability Year-in-Review

Sunday, March 21, 05:10 p.m. – 07:30 p.m. PDT Charlie Slayman, Cisco Systems

Venue: Monterey Main Stage

**Year-in-Review: Reliability Intro** 05:10 p.m. – 05:15 p.m. PDT

05·15 n m

YIR1 (Year-in-Review) - FinFET vs GAA: Main Reliability Differences and Concerns, Adrian Chasin, imec

FinFET devices have reigned in the last decade, allowing continuous scaling of silicon devices since first Intel adoption in the 22nm node up to the 5nm products recently released by TSMC. The adoption of a more

advanced architecture that can provide even better channel control and, therefore, allowing further scaling seems unavoidable. Gate-All-Around (GAA) devices were proposed as a natural follower and has been the focus of intensive research in the last years. Following a brief overview of the claimed performance advantages of such architecture, we will review the most recent reliability studies of this new device and how it compares to FinFETs. In particular, we will focus on new inherent features of this new technology and how they can impact the overall device reliability.

06:05 p.m.

YIR2 (Year-in-Review) - Reliability Testing: Considerations for Physics-Based Reliability Testing Development, Derek W. Slottke, Intel Corporation

Deviation from previous dependence on scaling based strategies of existing process technologies, the development of more diverse products, and pressures to minimize reliability margins are driving the need for a greater variation in available test capabilities. I hope to cover the considerations for volume reliability testing, challenges and trends, as well as some specific topics of personal interest where I believe substantial novel work should be done.

06:55 p.m.

(In cooperation with IEW)

YIR3 (Year-in-Review) - Industry Council on ESD Target Levels: Review of Achievements, Activities, and Initiatives, Charvaka Duvvury, ESD Consulting, Harald Gossner, Intel Corporation

The Industry Council on ESD Target Levels has been recommending realistic specifications for ESD to be compatible with high-speed circuit performance. This review will cover the key accomplishments of the Council that changed the industry qualification processes for ESD reliability. Also, an overview of the myriad of root causes that lead electrical overstress (EOS) damage and the notion of Absolute Maximum Rating (AMR) as it relates to probability of EOS during applications will be discussed.

### Monday, March 22

#### **Keynote 2**

Monday, March 22, 08:00 a.m. – 08:45 p.m. PDT Chris Connor, Intel Robert Kaplar, Sandia National Labs Venue: Monterey Main Stage

08:00 a.m.

KN2 (Keynote) - SiC MOSFET Reliability: An overnight success 30 years in the making, John Palmour, Wolfspeed, a Cree Company

The rapid adoption of SiC MOSFETs may seem like an overnight sensation, but it was actually more than 30 years in the making. It has required orders of magnitude improvements in performance, cost, availability and quality. Improved material defect densities and larger wafer diameters are lowering cost and are allowing higher current products that fit the needs of the battery electric vehicle market.

In the early days of SiC power device technology, it was thought that SiC MOSFETs could never achieve the reliability lifetimes required for commercial markets. However, the quality of oxides grown on SiC are now being shown to be on par with the best silicon devices. Measurements of TDDB, breakdown voltages, radiation resistance and other critically important tests for SiC MOS devices will be demonstrated, and the issue of bias temperature instability (threshold voltage shift) in actual application conditions will also be discussed.

#### 3A – PI (Process Integration)

Monday, March 22, 08:45 a.m. – 10:30 a.m. PDT Anisur Rahman, Intel Guido Sasse, NXP Semiconductors Mustapha Rafik, Aledia Venue: Big Sur

3A-Intro

08:45 a.m. - 08:50 a.m. PDT

08:50 a.m.

**3A.1 - Impact of Spacer Interface Charges on Performance and Reliability of Low Temperature Transistors for 3D Sequential Integration,** T. Mota Frutuoso, J. Lugo-Alvarez, X. Garros, L. Brunet, J. Lacord, L. Gerrer, M. Casse, E. Catapano, C. Fenouillet-Beranger, F. Andrieu, F. Gaillard, CEA, P. Ferrari, Univ. Grenoble Alpes

The impact of interface charges under the gate spacer on FDSOI devices integrated in low temperature process are explored. A great number of traps ( $\sim 10^{13} \, / \mathrm{cm^2}$ ) are identified on the interface between the spacer oxide and the silicon film using Terman's method for interface states characterization. Thanks to electrical characterization and TCAD simulations, it is shown that the trapped charges induce the formation of a depleted region in the vicinities of the spacer. Moreover, a strong degradation of performances on underlap channels is observed. The spacer charges influence on reliability measurements is finally explored.

09:15 a.m.

**3A.2 - Systematic Study of Process Impact on FinFET Reliability,** Rakesh Ranjan, Ki-Don Lee, Md Iqbal Mahmud, Mohammad Shahriar Rahman, Pavitra Ramadevi Perepa, Charles Briscoe Larow, Caleb Dongkyun Kwon, Maihan Nguyen, Minhyo Kang, Ashish Kumar Jha, Ahmed Shariq, Shamas Musthafa Ummer, Susannah Laure Prater, Samsung Austin Semiconductor, LLC, Hyunchul Sagong, HwaSung Rhee, Samsung Electronics, Korea

Reliability of Core and IO FinFET is extensively investigated with various process steps at Fin, Source/Drain, sacrificial Gate-Metal, and High-Pressure D2 Anneal. By modulating the process knobs, we quantified the effect of oxide traps (at bulk or interface) on reliability mechanisms of replacement metal gate (RMG). The results are summarized as a process-reliability optimization guideline.

09:40 a.m.

**3A.3 - TDDB Reliability in Gate-All-Around Nanosheet,** Huimei Zhou, Miaomiao Wang, Ruqiang Bao, Tian Shen, Ernest Wu, Richard Southwick, Jingyun Zhang, Veeraraghavan Basker, Dechao Guo, IBM Research Division

Time dependent dielectric breakdown (TDDB) reliability is studied on interfacial layer (IL)/high-K gate stack of Gate-All-Around Nanosheet (GAA-NS) N- and P-type Field Effect Transistors (FETs) with volume-less multiple threshold voltage (multi-Vt) integration scheme enabled by the dual dipoles (n-dipole and p-dipole). We report for the first time Key TDDB Modeling parameters: voltage acceleration exponent (VAE), Weibull slope ( $\beta$ ), and activation energy ( $E_a$ ) and show robust TDDB reliability in multi-Vt NS transistors enabled by different dipoles.

10:05 a.m.

**3A.4 - Process-Induced Charging Damage in IGZO nTFTs**, Gaspard Hiblot, Nouredine Rassoul, Lieve Teugels, Katia Devriendt, Adrian Vaisman Chasin, Michiel van Setten, Attilio Belmonte, Romain Delhougne, Gouri Sankar Kar, IMEC

In this work, charging damage induced by processing in 300mm FAB on Indium-Gallium-Zinc-Oxide (IGZO) n-type Thin Film Transistors (TFT) is investigated using antennae connected at different levels. A compounded degradation due to two different mechanisms is revealed. Plasma etch damage is found to degrade the gate oxide leakage and reliability, while CMP-related charging affects the conductivity of the extension regions of the transistor.

#### 3A - Authors' Corner

10:30 a.m. - 10:55 a.m. PDT

#### 3B – 5G (RF/mmW/5G Reliability)

Monday, March 22, 08:45 a.m. – 10:30 a.m. PDT Jose Jimenez, Qorvo Fernando Guarin, GlobalFoundries Venue: Carmel

#### 3B – Intro

08:45 a.m. - 08:50 a.m. PDT

08:50 a.m.

**3B.1** (Focus) - New Developments in SiGe HBT Reliability for RF Through mmW Circuits, John D. Cressler, School of Electrical and Computer Engineering

This paper reviews current progress in our understanding of the reliability of SiGe HBTs and the circuits built from them, including: 1) fundamental understanding of the multiple operative damage mechanisms, 2) the differences between DC and RF reliability, 3) the path to predictive reliability-aware compact models, and 4) the concept of Circuit- Safe Operating Area (C-SOA), which offers a better benchmark for understanding reliability-imposed constraints on circuits and systems.

09:15 a.m.

**3B.2** (Focus) - Reliability and Failure Analysis of 100 nm AlGaN/GaN HEMTs under DC and RF Stress, M. Dammann, M. Baeumler, T. Kemmer, H. Konstanzer, P. Brückner, S. Krause, Fraunhofer Institute for Applied Solid State Physics IAF, A. Graff, M. Simon-Najasek, Fraunhofer Institute of Microstructure of Materials and Systems

Degradation of 100 nm AlGaN/GaN HEMTs under DC and 10 GHz stress conditions has been compared and a promising median lifetime of more than 2000 h under RF stress in air at a drain voltage of 15 V and an average channel temperature of 230°C has been achieved. It has been found that the devices degrade faster under RF stress compared to DC stress. Physical failure analysis using electroluminescence, TEM and EDX has been done.

09:40 a.m.

**3B.3 - RF Reliability of SOI-Based Power Amplifier FETs for mmWave 5G Applications,** P. Srinivasan, F. Guarin, S. Syed, J. A. S. Jerome, W. Liu, S. Jain, D. Lederer, S. Moss, P. Colestock, A. Bandyopadhyay, N. Cahoon, B. Min, M. Gall, Globalfoundries Inc.

RF reliability at 28GHz in PAFETs under constant and varying output load (Z0) was evaluated. Time domain analyses show that in addition to non-conducting TDDB (ncTDDB), both onducting (cHCI) and non-conducting Hot Carrier Injection (ncHCI) degradation play key roles as primary mechanisms. RF power as stress variable under linear, P1dB and compression shows higher degradation in compression attributed to higher peak voltage swings. Degradation under varying load is correlated to ruggedness power and VSWR ratio.

10:05 a.m.

**3B.4 - Large Signal RF Reliability of 45-nm RFSOI Power Amplifier Cell for Wi-Fi6 Applications,** Aarti Rathi<sup>1</sup>, P.Srinivasan<sup>2</sup>, F.Guarin<sup>2</sup>, Abhisek Dixit<sup>1</sup>, 1. Indian Institute of Technology, 2. GLOBALFOUNDRIES Inc

A power amplifier cell having a single n-channel transistor fabricated in 45-nm RFSOI technology is stressed using both DC drain voltage as well as RF power at 7GHz applied to the gate reproducing Wi-Fi6 like operating conditions. Impact of the stress is studied using both DC as well as RF metrics. Impact on impedance matching is also studied using small signal characteristics. Through this work, we attempt to explore differences in hot carrier degradation mechanisms between DC and RF stress conditions. Impact of hot carrier degradation on DC and RF parameters is also presented by analyzing the time slope exponent. Degradation in DC and RF performance (small and large signal) is compared under varying stress conditions (DC, RF, and DC+RF).

#### 3B - Authors' Corner

10:30 a.m. – 10:55 a.m. PDT

#### **Tutorial 5**

Monday, March 22, 08:45 a.m. -10:15 a.m. PDT Jason Ryan, NIST

08:45 a.m.

TuT5 (Tutorial) - Neuromorphic Computing, Brian Hoskins, NIST

The different requirements of neuromorphic computers, including enormous demand for memory and a high tolerance for defects, is causing a reassessment of research priorities into integrated circuit manufacturing. We will review the foundations of the most important new computing approaches in A.I. and the ways these operations can be accelerated using nanotechnology for critical use cases, but especially for online training of networks as well as inference in the field where they will be deployed.

#### **Tutorial 6**

Monday, March 22, 08:45 a.m. – 10:15 a.m. PDT Marta Bagatin, University of Padova

08:45 a.m.

**TuT6** (**Tutorial**) - Calculation of Terrestrial Cosmic-Ray Displacement Damage, Melanie Raine, CEA, DAM, DIF, Nicolas Richard, CEA, DAM, DIF

Terrestrial neutrons due to cosmic rays from the outer space are constantly striking electronic devices at ground level. Each neutron is likely to generate a cascade of atomic displacement, that can be referred to as Single Particle Displacement Damage. With device integration, these single cascades might impact the properties of integrated devices. This tutorial presents a comprehensive approach for the simulation of Single Particle Displacement Damage, from the incident particle interaction to the resulting electrical effect observed experimentally. The different steps of the global approach are presented, first describing the succession of phenomena at stake, and then identifying the corresponding simulation technique chosen for each step of the process, some outputs of one step being the inputs of the next. Combining different techniques allows covering large time scales, from the fs for the interaction itself to long-term evolution observed after seconds and more.

Monte Carlo simulation of the interaction between an incident particle and silicon, in the Binary Collision Approximation (BCA) is first performed. The next step is a classical Molecular Dynamics (MD) simulation of the trajectory of selected Primary Knock-on Atoms (PKA), with the detailed displacement cascade and the

first steps of its evolution. To explore the long term evolution of this structure and reach time scales comparable with experimental data, a new technique called the kinetic Activation-Relaxation Technique (k-ART) is then used. Finally, first principles calculations are performed to calculate the electronics properties of the selected atomic damage structure. The output is, for each selected atomic damage structure, the energy levels introduced in the bandgap and the associated electronic activity. The originality of this comprehensive approach is to link these different types of simulations that are usually performed independently, to obtain realistic damage structures representative of what results from the initial neutron-silicon interaction and to identify defect structures detrimental to the technology's performances.

#### **Tutorial 7**

Monday, March 22, 10:15 a.m. – 11:45 a.m. PDT Bonnie Weir, Broadcom

10:15 a.m.

TuT7 (Tutorial) - Understanding and Challenges of MOL/BEOL TDDB Reliability, Andrew Kim, Intel

MOL (Middle-Of-Line) and BEOL (Back-End-Of-Line) dielectric reliabilities have become a great importance for advanced semiconductor process technology development and qualifications. Particularly, dielectric thickness variation effect on MOL/BEOL TDDB has become a severe issue to deal with in terms of characterization and lifetime modeling. This tutorial will begin with an introductory review of MOL/BEOL TDDB followed by various topics such as statistical modeling of Tbd (Time-to-Breakdown), thickness variation effect on Tbd, review of voltage acceleration models, requirements of voltage acceleration model validation, consideration for TDDB test device designs and advanced characterization/modeling methods. As supplemental characterization/screening methods of TDDB, ramped voltage stress (RVS) and ramped current stress (RCS) will also be discussed. Both entry-level and experienced TDDB reliability colleagues are strongly encouraged to attend.

#### **Tutorial 8**

Monday, March 22, 10:15 a.m. – 11:45 a.m. PDT Robert Kaplar, Sandia National Labs

10:15 a.m.

**TuT8** (**Tutorial**) - **GaN Reliability**, Enrico Zanoni, University of Padova, Department of Information Engineering, Padova

GaN HEMTs represent nearly ideal devices for high efficiency switching converters and power management systems, as well as for microwave and millimeter-wave communication apparatus and imaging systems. Power MISHEMT devices have attained blocking voltages of several hundred volts, yet maintaining extremely low values of on-resistance. By carefully controlling short-channel effects, sub-100 nm GaN microwave devices can achieve record values of RF power density and power added efficiency up to W-band. Mature, stable technologies have been demonstrated, with remarkable extrapolated lifetimes. Power and RF GaN HEMTs share common failure mechanisms (e.g. hot-electron effects and threshold voltage instabilities); specific failure mechanisms depend on operating conditions and environment, technology, material quality. Surface and interfaces play a dominant role in determining device reliability. In power devices, time-dependent breakdown mechanisms affect both dielectrics and GaN-based semiconductor epitaxial layers. For microwave devices, thermally accelerated interdiffusion effects and electrochemical oxidation still represent a potential issue. The tutorial will review failure mechanisms of GaN HEMTs in relation with high voltage operation, high current density, high electric field and hot-electrons, and compare their impact on the various device applications.

#### **Exhibitor Meet & Greet**

11:20 a.m. - 03:00 p.m. PDT

#### **Break**

12:05 p.m. – 03:00 p.m. PDT

#### 3D – SY/SE (System Electronics Reliability & Soft Error)

Monday, March 22, 03:00 p.m. – 05:10 p.m. PDT Flavio Griggio, Microsoft Daisuke Kobayashi, isas/jaxa Yan Liu, Medtronic Yanran Chen, Xilinx, Inc. Venue: Big Sur

#### 3D – Intro

03:00 p.m. – 03:05 p.m. PDT

03:05 p.m.

**3D.1** (Invited) - Single Event Hard Error Due to Terrestrial Radiation, Jin-Woo Han, M. Meyyappan, NASA Ames Research Center Moffett Field, Jungsik Kim, Gyeongsang National University

Alpha particle radioactive contamination is often found in semiconductor packaging materials, and neutrons generated by cosmic rays constantly approach the ground. Historically, these radiations are regarded as a source of soft-error. We are in era of aggressive device miniaturization, operation voltage scaling and increasing frequency. Herein, we present that the terrestrial radiation-induced single event can potentially result in hard-error. As a result, radiation hardening might be necessary in the near future even in consumer electronics.

03:30 p.m.

**3D.2 - Scaling Trends in the Soft Error Rate of SRAMs from Planar to 5-nm FinFET,** B. Narasimham, V. Chaudhary, M. Smith, L. Tsau, Broadcom Inc, D. Ball, B. Bhuva, Vanderbilt University

SRAM SER measurements across technology nodes indicate that while scaling from planar processes down to the 7-nm FinFET process provided a reduction in the per-bit SER at every node, subsequent scaling to the 5-nm FinFET process results in an increase in the per-bit SER relative to the 7-nm FinFET process. Extensive data collected across a range of supply voltages show strong exponential bias dependence of SRAM SER for FinFET processes, but the rate of increase in SER as supply voltage is reduced is lower for the 5-nm process compared to the 7-nm. Simulations and modeling indicate that variations in the critical charge ( $Q_{crit}$ ) is the key reason for the observed trends.

03:55 p.m.

**3D.3 - Soft-Error Suseptability in Flip-Flop in EUV 7 nm Bulk-FinFET Technology,** Taiki Uemura, Byungjin Chung, Jeongmin Jo, Mijoung Kim, Dalhee Lee, Gunrae Kim, Seungbae Lee, Taesjoong Song, Hwasung Rhee, Brandon Lee, Samsung Electronics, Jaehee Choi, Semiconductor Research and Development Center

This paper presents single-event upset (SEU) rates in flip-flops (FFs) in EUV 7 nm bulk-FinFET technology. EUV technology achieves high transistor-density, small FF cell-size, and low SEU rate. The alpha-SEU rate in EUV 7 nm FFs is 0.7X of the SEU rates in 10 nm FFs. The neutron-SEU rate in EUV 7 nm FFs is 0.6X of the SEU rates in 10 nm FFs. This paper also discusses the circuit dependence of the SEU rate in Normal-, Reset-, Set-FFs, and a soft-error immune FF (SEIFF), and SRAM.

04:20 p.m.

**3D.4 - A Study on System Level UFS M-PHY Reliability Measurement Method using RDVS,** NamHyuk Yang<sup>1</sup>, JinHwan Kim<sup>1</sup>, GeonGu Park<sup>1</sup>, ChulHyuk Kwon<sup>1</sup>, SeungTaek Lee<sup>1</sup>, SangWoo Pae<sup>1</sup>, HooSung Kim<sup>1</sup>, SangWon Hwang<sup>1</sup>, 1. Samsung Electronics

With the development of high speed serial interface technology, data transmission speed is increasing and it is important to secure the signal transmission quality. In particular, in the case of smartphones, the signal compatibility of the physical layer (M-PHY) is critical with various application processors (AP) and devices communicating eachother. This study proposes a method for verifying M-PHY reliability similar to the actual user environment based on a Universal Flash Storage (UFS) used in smartphone.

04:45 p.m.

**3D.5** - Reliability Characterization of a Flexible Interconnect for Cryogenic and Quantum Applications, Emma R. Schmidgall, Flavio Griggio, George H. Thiel, Microsoft Corporation Redmond, Sherman E. Peek, Bhargav Yelamanchili, Archit Shah, Vaibhav Gupta, John A. Sellers, Michael C. Hamilton, Department of Electrical and Computer Engineering/Alabama Micro/Nano Science and Technology Center, David B. Tuckerman, Tuckerman & Associates, Samuel d'Hollosy, Hightec MC AG

We present reliability characterization of a polyimide/copper-based flexible interconnect designed for cryogenic and quantum computing applications. This interconnect design uses commercial fabrication processes and off-the-shelf parts. This paper presents results from the flexible interconnects bonded to a commercial connector part. A model is described to estimate a system failure rate due to interconnect and connector subassembly failures. The results of this study conclude that the flexible interconnect tapes are well suited for cryogenic temperature applications.

#### 3D - Authors' Corner

05:10 p.m. – 05:30 p.m. PDT

#### 3E – 5G (RF/mmW/5G Reliability)

Monday, March 22, 03:00 p.m. – 04:45 p.m. PDT Fernando Guarin, GlobalFoundries Jose Jimenez, Qorvo Venue: Carmel

#### 3E – Intro

03:00 p.m. – 03:05 p.m. PDT

03:05 p.m.

**3E.1 - CMOS RF Reliability for 5G mmWave Applications – Challenges and Opportunities,** P. Srinivasan, F. Guarin, GLOBALFOUNDRIES Inc

CMOS RF technologies are now entering mainstream due to opportunities presented by 5G technologies. RF Front-End-Module designs to enable 5G mmWave applications focus on performance and efficiency RF metrics. One key element that also requires focus and attention is RF reliability. This work will focus on key challenges in evaluating RF reliability at device and circuit level and the opportunities that exist towards meeting these requirements to enable successful designs.

03:30 p.m.

**3E.2** (Focus) - Guidelines for Space Qualification of GaN HEMTs and MMICs, John Scarpulla, The Aerospace Corporation

GaN HEMTs and MMICs are candidates for use in space systems because of their many advantages especially as RF/microwave amplifiers. To date however, no GaN devices have successfully been qualified high reliability, long duration missions. The purpose of this paper is to recommend GaN-specific test protocols and guidelines to attempt to amend this situation. A document expanding upon this paper is now available, and a working group continues to refine it.

03:55 p.m.

**3E.3 - On the Impact of Buffer and GaN-Channel Thickness on Current Dispersion for GaN-on-Si RF/mmWave Devices,** V. Putcha<sup>1</sup>, L. Cheng<sup>2</sup>, A. Alian<sup>1</sup>, M. Zhao<sup>1</sup>, H. Lu<sup>2</sup>, B. Parvais<sup>1,3</sup>, N. Waldron, D. Linten<sup>1</sup>, N. Collaert<sup>1,1</sup>imec, <sup>2</sup>Nanjing University, <sup>3</sup>Vrije Universiteit Brussels

An important degradation monitor for GaN-on-Si technology is the current dispersion, resulting from charge (de-)trapping into the defects in the buffer stack or the barrier layer. It is commonly monitored as device's ON-resistance (R ON). In this work, a detailed study of the impact of buffer thickness and the GaN-channel layer thickness on the dynamic- R ON is carried out and important insights that are useful for optimizing the buffers for GaN-on-Si technology are obtained.

04:20 p.m.

**3E.4 - Role of the AlGaN Cap Layer on the Trapping Behaviour of N-Polar GaN MISHEMTs,** F. Chiocchetta, C. Calascione, C. De Santi, C. Sharma, F. Rampazzo, X. Zheng, B. Romanczyk, M. Guidry, H. Li, S. Keller, U. K. Mishra, G. Meneghesso, M. Meneghini, E. Zanoni, 1. University of Padova, Department of Information Engineering, 2. University of California Santa Barbara

We investigate the performance of N-polar GaN MIS-HEMT devices as a function of the aluminum concentration in the top AlGaN cap layer. It is demonstrated that the use of high aluminum concentration in the cap layer results a lower gate leakage current. It's also shown that the use of high Al concentration can suppress the current collapse. The results points out the key role of the AlGaN cap layer on the performance of AlGaN-based MISHEMTs.

#### 3E - Authors' Corner

04:45 p.m. – 05:10 p.m. PDT

#### **3F – MB (Metallization/BEOL Reliability)**

Monday, March 22, 03:00 p.m. – 05:10 p.m. PDT Rahim Kasim, Intel Corporation Venue: Pebble Beach

#### 3F - Intro

03:00 p.m. – 03:05 p.m. PDT

03:05 p.m.